RP 10322 CENTRE NATIONAL D'ETUDES

CENTRE NATIONAL D'ETUDES DES TELECOMMUNICATIONS

CENTRE NATIONAL DE LA RECHERCHE SCIENTIFIQUE

CENTRE DE RECHERCHES EN PHYSIQUE DE L'ENVIRONNEMENT TERRESTRE ET PLANETAIRE

NOTE TECHNIQUE CRPE / 187

FILTRAGE RIF RAPIDE:

ALGORITHMES ET ARCHITECTURES

1NGE (4210)

Par

Z.J. MOU

INSTITUT DE L'INFORMATION SCIENTIFIQUE ET TECHNIQUE

2. Alile du Parc de Brabois - Tél. 83.50.46.00 INIST - 54514 VANDŒUVRE LÊS NANCY CEDEX

RPE/ETP 38-40, rue du Général Leclerc 92131 ISSY-LES-MOULINEAUX.FRANCE

# CENTRE DE RECHERCHES EN PHYSIQUE DE L'ENVIRONNEMENT TERRESTRE ET PLANETAIRE

**NOTE TECHNIQUE CRPE/187**

# FILTRAGE RIF RAPIDE : ALGORITHMES ET ARCHITECTURES

par

Z.J. MOU RPE/ETP

38-40 rue du Général Leclerc 92131 ISSY-LES-MOULINEAUX

Le Directeur

6. SOMMERIA

Le Pirecteur Adjoint

J.J. BERTHELIER

#### CNET

MM POITEVIN Directeur du CNET Directeur Adjoint THABARD du CNET COLONNA Adjoint Militaire au Directeur du CNET MERLIN Directeur des Programmes DICET BLOCH THUE DICET HENAFF MME DICET MM. PIGNAL PAB PAB RAMAT NOBLANC PAB-BAG ABOUDARHAM PAB-SHM HOCQUET PAB-STC **THEBAULT** PAB-STS PAB-RPE MME PARTS MM. BAUDIN PAB-RPE BERTHELIER PAB-RPE PAB-RPE BIC CERISIER PAB-RPE PAB-RPE GENDRIN **LAVERGNAT** PAB-RPE ROBERT PAB-RPE ROUX PAB-RPE SOMMERIA PAB-RPE TESTUD PAB-RPE PAB-RPE VIDAL-MADJAR

#### CNRS

BERROIR MM. TOAE CHARPENTIER SPI MME SAHAL TOAE COUTURIER MM. INSU MME LEFEUVRE AD3 M. DUVAL AD5

## CNES

MMES AMMAR

DEBOUZY

MM. BAUDOIN

FELLOUS

HERNANDEZ (Toulouse)

#### **Bibliothèques**

CNET-SDI (3)

CNET-EDB

CNET-RPE (Issy) (5)

CNET-RPE (St Maur) (2)

Observatoire de Meudon

CNRS-SA

CNRS-INIST

CNRS-LPCE

#### LAA/TSS/CMC **COMBESCURE** LAA/TSS/CMC **GILLOIRE** LAA/TSS/CMC LAMBLIN LAA/TSS/CMC PETT LAA/SLC/BSA **HERVE** LAA/RSM/SIM HAMIDI RIDHA **RENAN** LAB/MER/STA LAB/SMR/TCM **JONCOUR** LAB/IFE/CIP TREGUIER MAITRET PAB/STC/PSN PAB/SHM/SMC TORTELIER PAB/RPE/ETP BENESTY PAB/RPE/ITS **CELIN**

#### **CNS - GRENOBLE**

| ARNDT    |

|----------|

| WITTMANN |

| BALESTRO |

| MAGINOT  |

| PRIVAT   |

| ROUQUIER |

|          |

#### **CCETT - RENNES**

| STM/TRM       | LEMAUVIEL  |

|---------------|------------|

| SRL/MNC       | LESAFFRE   |

| SRL/MTT       | PALICOT    |

| SRL/MTT       | LANOISELEE |

| DOCUMENTATION |            |

#### **EXTERIEUR**

| ENST<br>ENST | BARRAL<br>GRENIER |

|--------------|-------------------|

| ENST         | MOU               |

| ENST         | RENARD            |

| ENST         | BIBLIOTHEQUE      |

### **RESUME**

Le filtre à réponse impulsionnelle finie (RIF) joue un rôle des plus importants dans le traitement numérique du signal et représente souvent la principale charge de calcul dans une application soit en logiciel soit en matériel.

Cette thèse est divisé en deux parties. La première partie de la thèse traite le problème de la réduction de la complexité arithmétique du filtre RIF. Nous fournissons un ensemble d'algorithmes permettant de 'casser' le filtre habituel en plusieurs sous-filtres échantillonnés, de telle manière que le nombre d'opérations à effectuer se trouve réduit. La deuxième partie étudie non seulement l'implantation de ces sous-filtres mais plus généralement l'architecture des filtres RIF en vue de leur intégration VLSI.

Nous présentons une approche unifiée pour tous les algorithmes rapides de filtrage RIF. Le théorème du reste chinois (TRC) constitue la base de l'approche. Tout d'abord nous formulons le filtrage RIF comme un produit polynomial. Ensuite l'application du TRC se fait en trois étapes: 1) interpolation; 2) filtrage; 3) reconstruction. L'approche se termine par le recouvrement. Sous une présentation pseudocyclique, il est facile de démontrer quelques propriétés utiles des algorithmes. Les algorithmes classiques sont examinés dans ce cadre. Mais l'unification de ces algorithmes n'est pas notre seul objectif. Nous présentons aussi des nouvelles possibilités apportées par cette approche, qui permet d'établir en particulier tous les algorithmes intermédiaires entre traitements temporels et fréquentiels. Nous traitons les algorithmes de petite longueur en détail. Ces algorithmes permettent de réduire la complexité arithmétique en gardant comme brique de base des filtres RIF d'ordre plus petit. Ils sont donc ouverts à diverses implantations.

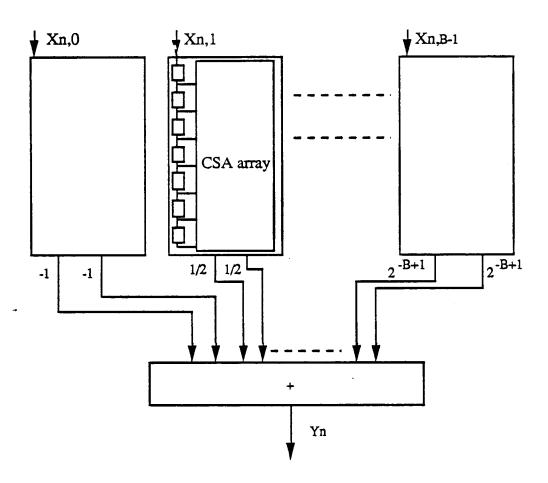

Nous étudions ensuite l'aspect arithmétique du multiplieur-accumulateur d'une part, et de nouvelles architectures d'autre part. Une conception compacte et régulière de l'arbre de Wallace est proposée pour surmonter les difficultés qui empêchaient l'application de cette structure par ailleurs très efficace au niveau du temps de calcul. Nous présentons quelques nouveaux accumulateurs rapides. L'architecture du filtre RIF par l'arithmétique distribuée est analysée en détail. Nous présentons de nouvelles structures ayant les caractéristiques suivantes: sans ROM; avec l'additionneur carry-save comme brique de base; avec accumulation rapide. En particulier, un nouveau codage est proposé pour profiter de la symétrie des coefficients afin de réduire la quantité de matériel et d'accélérer le calcul.

## **SUMMARY**

The finite impulse response (FIR) filter plays one of the most important roles in digital signal processing. It often represents the major computational load in a system either in software or in hardware.

The dissertation is divided in two parts. The first part deals with the problem of reducing the arithmetic complexity in FIR filtering. We present a class of algorithms allowing to "cut" a usual filter into several subfilters in such a way that the number of operations is reduced. The second part studies not only the implementation of these subfilters but more generally the architecture of FIR filters for Very Large Scale Integration (VLSI).

We present a unified approach to all the fast FIR filtering algorithms. The Chinese Remainder Theorem (CRT) constitutes the basis of the approach. First of all, we formulate the FIR filtering equation as a polynomial product. Then the application of CRT is made in three steps: 1) interpolation; 2) fitering; 3) reconstruction. The approach finishes by overlapping. Under a pseudocyclic presentation, some interesting properties of algorithms are demonstrated. The classical FIR filtering algorithms are examined in the context of this approach. But the unification of all the FIR filtering algorithms is not our only objective. We present also several new possibilities promised by the approach, which in particular allows to establish all the intermediate algorithms between processings in time and in frequency domain. We explain the short-length FIR filtering algorithms in detail. These algorithms allow to reduce the arithmetic complexity while maintaining moderate-length FIR filters as building blocks. Hence they are open to various implementations.

Our study is then concerned with the arithmetic aspect in one hand and new architectures in the other hand for VLSI implementation of FIR filters. Some improved structures are presented for Wallace-tree and fast accumulators. The distributed arithmetic implementation of FIR filters is also analyzed in more detail. We propose new structures having the following characteristics: without ROM; with carry-save adder as building block; with fast accumulators. In particular a new encoding technique is suggested for implementing symmetric FIR filters.

(Les pages 1 à 132 correspondent à une rédaction détaillée en anglais des résultats obtenus. Les pages 133 à 165 en donnent une version concise en français.)

# **Table of Contents**

| Chapter   | 1                                                                    |

|-----------|----------------------------------------------------------------------|

| Introduct | ion1                                                                 |

| 1.1       | FIR filtering algorithms                                             |

| 1.2       | FIR filter architectures4                                            |

| 1.3       | Terminology and remarks                                              |

| Chapter   | 2                                                                    |

| A unified | approach to the fast FIR filtering algorithms                        |

| 2.1       | Formulation of FIR filtering as a polynomial product 8               |

| 2.2       | Fast computation of a polynomial product                             |

|           | 2.2.1 The Chinese Remainder Theorem                                  |

|           | 2.2.2 Interpolation                                                  |

|           | 2.2.3 Filtering                                                      |

|           | 2.2.4 Reconstruction by the CRT11                                    |

| 2.3       | Overlap12                                                            |

| 2.4       | Pseudocyclic convolution                                             |

|           | 2.4.1 Diagonalization of a pseudocirculant matrix14                  |

|           | 2.4.2 Transposition of an F(N,N) algorithm14                         |

|           | 2.4.3 Identical arithmetic complexity in direct and transposed forms |

| 2.5       | Remarks 18                                                           |

| Chapter 3                                                    | 19 |

|--------------------------------------------------------------|----|

| Review on the FIR filtering algorithms and new possibilities | 19 |

| 3.1 Review on the classical algorithms                       | 19 |

| 3.1.1 FFT-based algorithms                                   | 20 |

| 3.1.2 Algorithms using aperiodic convolutions                | 22 |

| 3.1.3 Winograd algorithms                                    | 25 |

| 3.2 Short length FIR filtering algorithms                    | 28 |

| 3.3 Shorter FFT-based algorithms                             | 29 |

| 3.4 Short length complex FIR filtering algorithms            | 33 |

| 3.5 Remarks                                                  | 37 |

| Chapter 4                                                    | 41 |

| Short length FIR filtering algorithms                        | 41 |

| 4.1 Introduction                                             | 41 |

| 4.2 Article 1                                                | 42 |

| 4.3 Article 2                                                | 50 |

| Chapter 5                                                    | 79 |

| Fast multiplier-accumulator                                  | 79 |

| 5.1 Multiplier-accumulator                                   | 79 |

| 5.2 Reduction of the number of partial products              | 79 |

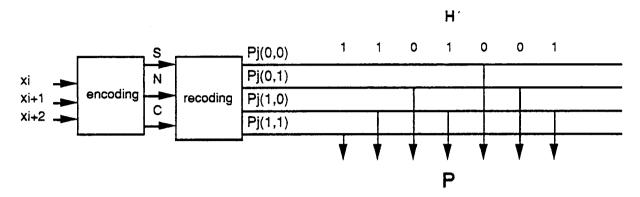

| 5.2.1 Booth's encoding                                       | 80 |

| 5.2.2 The modified Booth's encoding (MBE)                    | 81 |

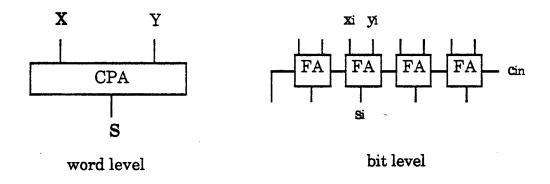

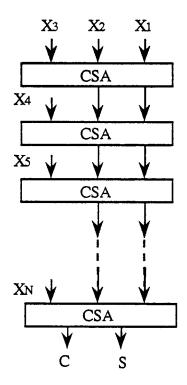

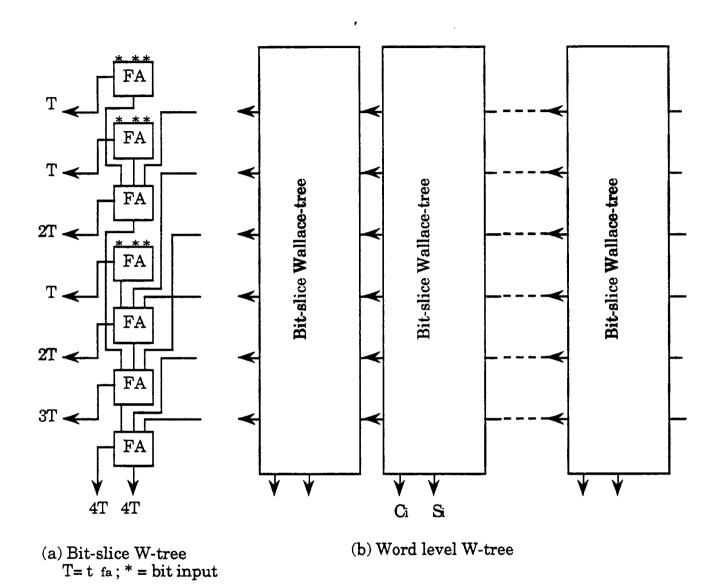

| 5.3 Multioperand summation                                   | 83 |

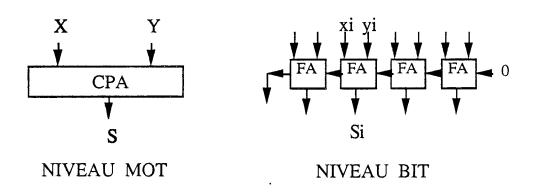

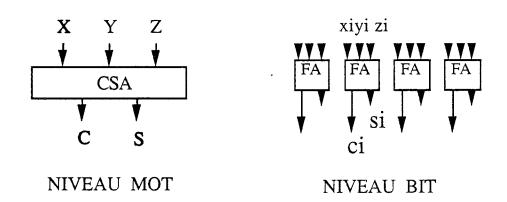

| 5.3.1 Using carry-save adder (CSA)                           | 83 |

|                                                              |    |

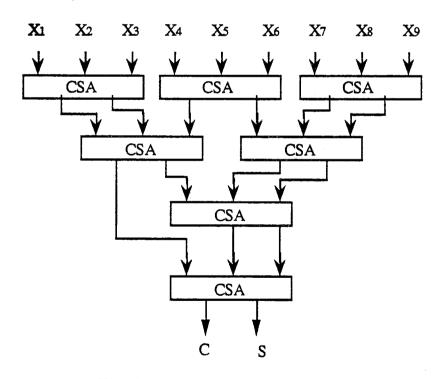

| 5.3.2 Wallace-tree and its compact layout85                             |

|-------------------------------------------------------------------------|

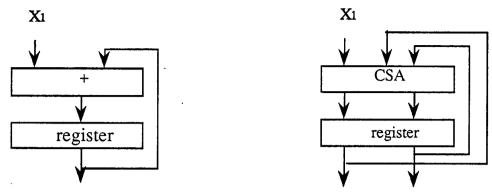

| 5.4 Fast accumulator88                                                  |

| 5.4.1 Carry-save (uni-operand) accumulator89                            |

| 5.4.2 Bi-operand and multi-operand accumulator90                        |

| 5.5 Pipelined multiplier-accumulator and new schemes92                  |

| 5.6 Remarks95                                                           |

| Chapter 6                                                               |

| New results on the distributed arithmetic implementation of FIR filters |

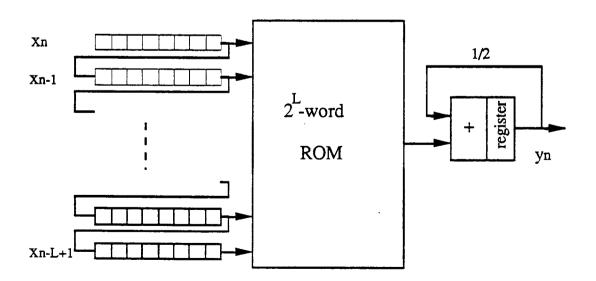

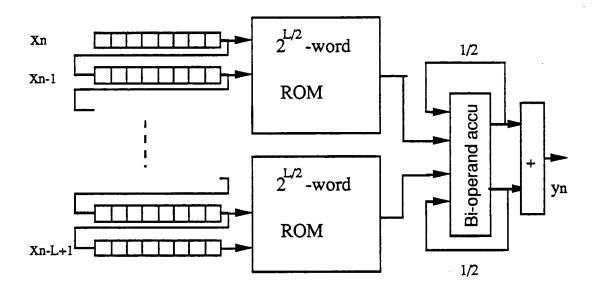

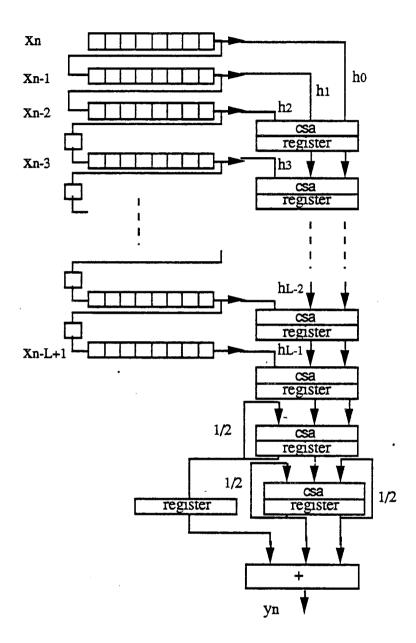

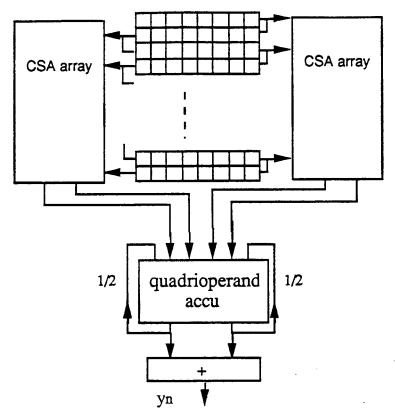

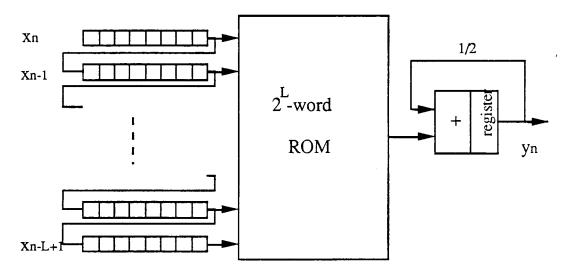

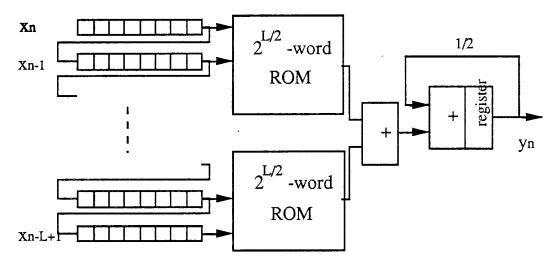

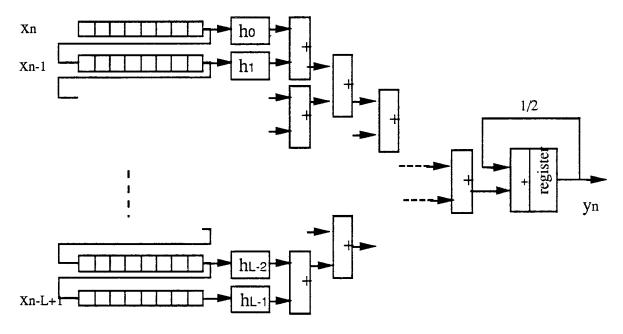

| 6.1 The principle of distributed arithmetic98                           |

| 6.2 New structures of general FIR filters                               |

| 6.2.1 Fast accumulation                                                 |

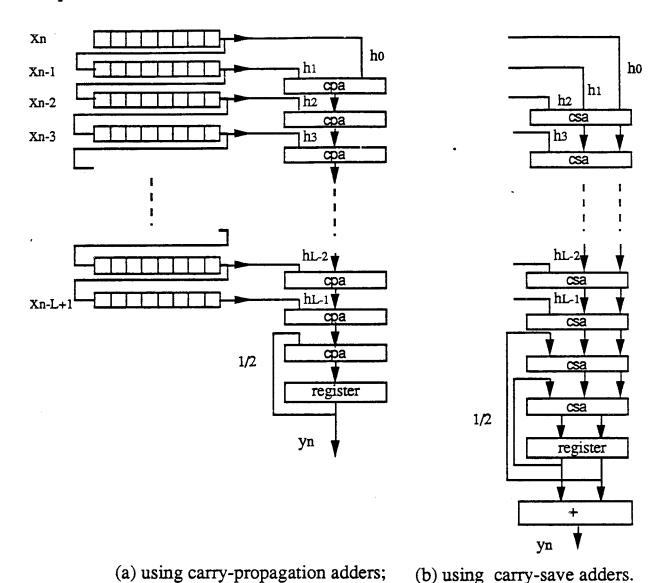

| 6.2.2 Adder-based structures                                            |

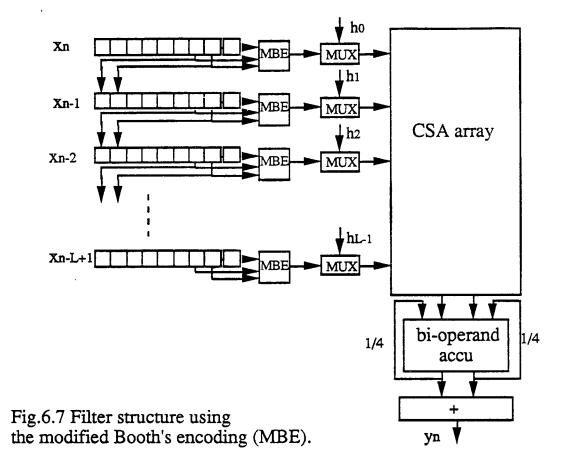

| 6.2.3 Using the modified Booth's encoding 105                           |

| 6.3 Symmetric FIR filters                                               |

| 6.3.1 Direct implementation                                             |

| 6.3.2 Using a new encoding                                              |

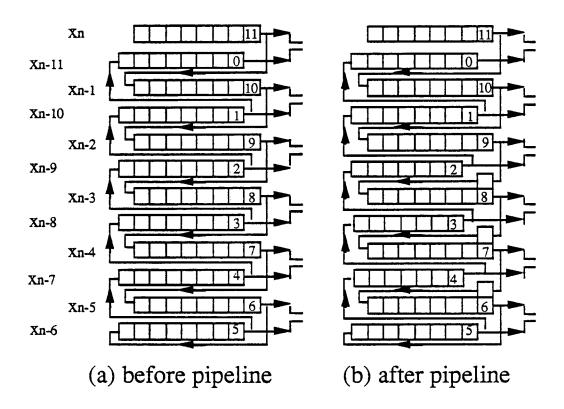

| 6.3.3 Pipelining                                                        |

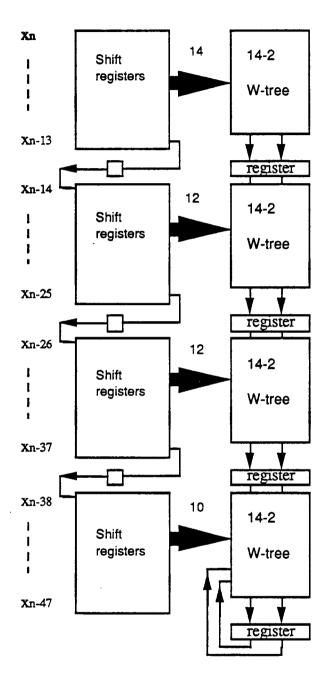

| 6.4 Bit-parallel implementation                                         |

| 6.4.1 Bit-slice approach                                                |

| 6.4.2 Symmetric FIR filters                                             |

| 6.5 Remarks                                                             |

| Chapter 7                                                               |

| Conclusion and perspectives                                                        |  |  |

|------------------------------------------------------------------------------------|--|--|

| 7.1 Conclusion                                                                     |  |  |

| 7.2 Perspectives                                                                   |  |  |

| 7.2.1 Multiprocessor implementation of FIR filters 116                             |  |  |

| 7.2.2 Application of fast FIR filtering algorithms to LMS adaptive filters         |  |  |

| 7.2.3 Silicon compiler for FIR filter implementation 117                           |  |  |

| Appendix119                                                                        |  |  |

| Fixed-point error analysis of short-length FIR filtering algorithms 119            |  |  |

| 1. Major assumptions119                                                            |  |  |

| 2. Quantization error in direct FIR filter computation 121                         |  |  |

| 3.Illustrative example for error analysis in short-length FIR filtering algorithms |  |  |

| 3.1 Analysis for direct radix-2 algorithm 121                                      |  |  |

| 3.2 Analysis for transposed radix-2 algorithm 122                                  |  |  |

| 3.3 Consideration for reduction of errors                                          |  |  |

| 3.4 Error analysis for quantization of coefficients                                |  |  |

| 4. Conclusion                                                                      |  |  |

| References                                                                         |  |  |

| Version concise en français                                                        |  |  |

# Chapter 1

# Introduction

The finite impulse response (FIR) filter plays one of the most important roles in modern digital signal processing. It exhibits some nice properties:

- 1)allowing linear phase implementation so that there is no phase distortion after filtering;

- 2) stability;

- 3) arbitrary approximation to any frequency response;

- 4) good quantization performance.

These properties make the FIR filter widely used in a large number of applications, for example, the telecommunications. However the main disadvantage of the FIR filter is the requirement of a great number of arithmetic operations in both software and hardware implementations.

The first part of this thesis is concerned with the problem of reducing the arithmetic complexity of FIR filters. The main issue is to construct and implement fast algorithms.

Since digital signal shows better performance than analog signal in diverse aspects such as precision, sensitivity to environment, conservability, etc., many traditional analog devices are being replaced by digital ones. However digital devices run in general more slowly than their analog counterparts. As real time signal processing requires higher and higher speed, another question arises: how to design a high speed FIR filter? A study on this problem constitutes the second part of the thesis.

## 1.1 FIR filtering algorithms

In the mid-60 the rediscovery of fast Fourier transform (FFT) algorithm by Cooley and Tukey [Coo65] has changed the world of digital signal processing. It is soon realized that FIR filters can be computed efficiently through FFT [Sto66]. Stockham's algorithm seems to be the earliest fast FIR filtering algorithm. This algorithm still enjoys a great popularity, if not the greatest. Agarwal and Burrus [Aga74] proposed some fast aperiodic

convolution algorithms for FIR filtering. Their algorithms are characterized by direct yet fast computation instead of transformation. Winograd [Win80] also presented an original class of FIR filtering algorithms without transformation. At the same time he gave the lower bound of the arithmetic complexity of computing an FIR filter.

The main feature in these algorithms is to compute N consecutive outputs together so that redundancy between N computations can be removed. It is tacitly assumed that N is not smaller than the filter's length. These algorithms were derived and tended to be optimized under such an assumption that a multiplication costs much more time than an addition.

The progress in semiconductor and computer technologies has altered the criteria for a fast algorithm. Multiplication time is no longer dominant in modern computers. For example in the widely used TMS320 Digital Signal Processor series, a multiplication plus an accumulation requires the same time as an addition alone does. However the classical FIR filtering algorithms are not suitable for implementation on these processors, because of their complex structure. The need for algorithms not only computationally efficient but also structurally implementable emerges.

This is our motivation to present a new class of FIR filtering algorithms [Mou87]. These algorithms are also proposed independently by other authors for implementation using filter banks [Vet88] or in VLSI [Kwa87]. They present a number of good properties such as arithmetic operation reduction and regular structure, particularly suitable for real time signal processing.

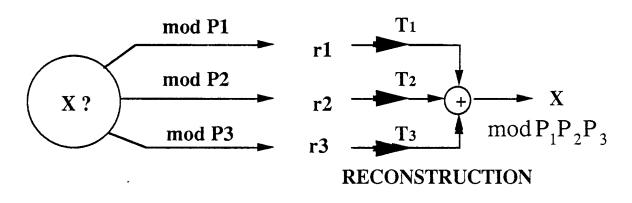

All these algorithms appear quite different from each other. Nevertheless they inherently belong to the same class of algorithms. In Chapter 2, we present a unified approach to the fast FIR filtering algorithms. The Chinese Remainder Theorem (CRT), which is well known for deriving fast polynomial product algorithms, constitutes the basis for that approach.

First of all, we show that the FIR filtering can be formulated as an polynomial product. Then the application of the CRT takes place in three steps: 1) interpolation; 2) filtering (multiplication in wide sense); 3) reconstruction. Finally overlapping is performed to get the filter's output. Overlap in FIR filtering algorithms differs them from other convolution algorithms. By taking into account the overlap, we may further reduce the number of operations. The FIR filtering algorithms thus constructed are in the form of a

pseudocyclic convolution: a pseudocirculant matrix [Vai88] multiplied by a vector. All the fast algorithms can be seen as a diagonalization of the pseudocirculant matrix. Under the pseudocyclic convolution, we can prove easily certain useful properties of the algorithms such as transposition and identical complexity in both direct and transposed form.

In Chapter 3, the classical algorithms of Stockham, Agarwal&Burrus, and Winograd will be reviewed in the light of the approach. Their derivations, relations to each other will be addressed, leading to a better understanding of the advantages as well as the limits of these algorithms. However the unification of the algorithms is not our unique objective. We will show some new possibilities promised by the approach, which in particular allows to establish all the intermediate algorithms between processing in frequency and in time. Among them, three types of algorithms are of special interest: shortlength FIR filtering algorithms (SLFIR), shorter-FFT based algorithms (SFFTA) and short length complex FIR filtering algorithms (SLCFIR). The first one reduces the arithmetic complexity by maintaining the multiplyaccumulate structure, which is suitable for many implementations. SFFTA allows to establish a number of algorithms meeting various trade-offs between arithmetic complexity, structural regularity and system delay. SLCFIR algorithms are the complex counterpart of SLFIR, suitable for fast complex FIR filtering. The combination of SFFTA and SLCFIR will result in some algorithms requiring less operations than the classical FFT-based ones, a fact going to the opposite of the general belief that the latter is the most efficient for large block processing.

Chapter 4 deals with the short length FIR filtering algorithms (SLFIR) in a detailed manner, based on two articles of the author (joint with P.Duhamel) [Mou87,Mou89]. These algorithms compute together a few number of filter outputs, allowing reducing the arithmetic complexity while maintaining smaller FIR filters as computing kernels. Hence, they are open to a wide range of implementations, including Digital Signal Processors (DSP's), VLSI, and even general purpose computers. The inherent parallelism of the algorithms allows also single-instruction-multiple-data (SIMD) multiprocessor implementation. General rules are provided for combining several SLFIR algorithms to construct composite length FIR filtering algorithms. Their arithmetic complexities are evaluated and compared to FFT based algorithms under various criteria.

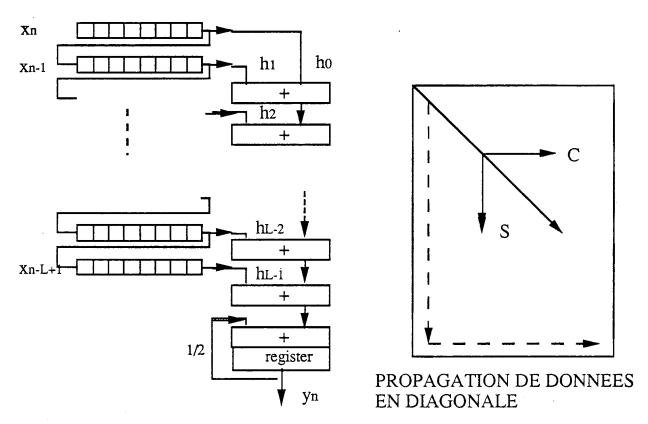

### 1.2 FIR filter architectures

The VLSI technology has greatly boosted the implementation of the digital devices. As emphasized by the title of the thesis, our device of interest is the FIR filter. There are various ways of implementing an FIR filter. For low speed applications, such as speech processing, we use mostly Digital Signal Processors where the principal working horse is a multiplier-accumulator. For high speed applications, such as telecommunications, we should fully integrate an FIR filter either in bit serial or in bit parallel methodology. The architecture is very important to an IC implementation. It predominates the speed and design complexity which are essential to a realization. Moreover in the first part the new filtering algorithms require FIR filters as building blocks. Thus we consecrate the second part to the study of some architectures for an FIR filter.

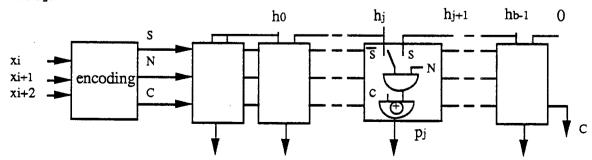

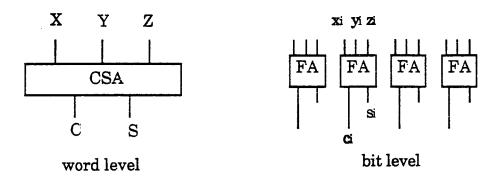

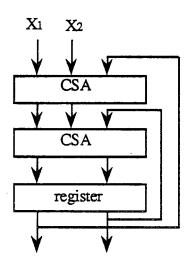

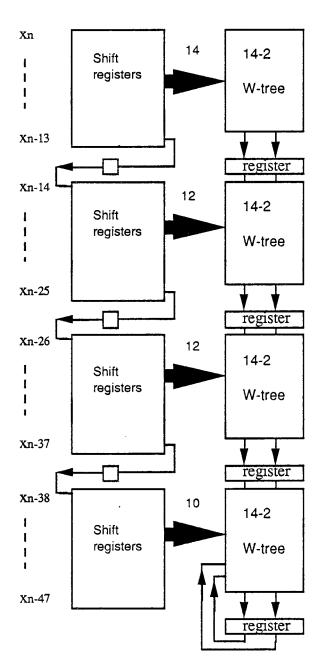

Chapter 5 is devoted to the review of arithmetic aspects of multiplier accumulator design and the investigation of new schemes. This study also serves as preparation for the subsequent chapters. We will review the reduction of partial products using Booth's encoding [Boo51] and the modified Booth's encoding [Mac61], summing of multiple operands using carry-save array and Wallace tree [Wal64], and fast accumulators. A compact yet regular Wallace tree design is proposed to overcome a belief that Wallace tree is not practical or not implementable [Vui81,Mon88]. Some new accumulators will be presented which allow faster implementation than ever known architectures to date.

Chapter 6 addresses the distributed arithmetic implementation of digital filters. It is often characterized by a lookup table or a ROM [Cro73,Bur77]. As the technology evolves, the ROM becomes the bottleneck to speed and occupies large chip area. We will present some new structures having following features: without ROM, massive use of carry-save adders and Wallace tree, and fast accumulation. Symmetric FIR filter is widely used for obtaining linear phase in signal processing. Its implementation can be further simplified owing to the symmetric coefficients. The architectures of symmetric filter is particularly studied. A new encoding is proposed to increase the speed both in bit serial and in bit-parallel design. Fully parallel implementation of FIR filter is also addressed. The new encoding proves to be more efficient than the modified Booth's encoding for parallel symmetric filter implementation.

Chapter 7 concludes the thesis and discusses the future research directions.

## 1.3 Terminology and remarks

For the sake of a clear presentation, it is necessary to clarify certain terminologies. It is often confused between linear convolution, cyclic convolution, aperiodic convolution, polynomial product and FIR filtering. What are their relations and their differences? We begin our explanation by stating their differences:

a) linear convolution, aperiodic convolution, polynomial product are the same operation on two finite length sequences: one of length M, the other of length N. Their computation are often expressed as a polynomial product of a (M-1)-degree polynomial and a (N-1)-degree one:

$$\begin{aligned} y_0 + y_1 z + y_2 z^2 + ... + y_{M+N-1} z^{M+N-1} \\ &= (h_0 + h_1 z + h_2 z^2 + ... + h_{M-1} z^{M-1})(x_0 + x_1 z + x_2 z^2 + ... + x_{N-1} z^{N-1}) \end{aligned} \tag{1.1}$$

The result is a sequence of M+N-1 numbers. In the sequel, only the terms "aperiodic convolution" (AC in short) and "polynomial product" are employed. When M=N, we often call it a radix-M aperiodic convolution or polynomial product.

b) cyclic convolution is an operation on two sequences of equal length M. Under polynomial presentation, it is well illustrated by the product of two (M-1)-degree polynomials modulo  $(z^{M}-1)$ :

$$\begin{aligned} &y_0 + y_1 z + y_2 z^2 + ... + y_{M-1} z^{M-1} \\ &= (h_0 + h_1 z + h_2 z^2 + ... + h_{M-1} z^{M-1})(x_0 + x_1 z + x_2 z^2 + ... + x_{M-1} z^{M-1}) \ \text{mod}(z^M - 1)_{(1.2)} \end{aligned}$$

The result is also a sequence of M numbers. We will term it as length-M cyclic convolution.

c) FIR filtering is an operation on two sequences: an infinite one and a finite one of length M. Using z-transform, it can be formulate as a product of two polynomials: one of infinite degree, the other of degree M-1.

$$y_0 + y_1 z + y_2 z^2 + \dots$$

$$= (h_0 + h_1 z + h_2 z^2 + \dots + h_{M-1} z^{M-1})(x_0 + x_1 z + x_2 z^2 + \dots)$$

(1.3)

The result is an infinite sequence. This operation is referred to as length-M FIR filtering.

Although the three operations are quite different from each other, they are closely related:

- 1) an aperiodic convolution of a length-M sequence and a length-N one can be computed by a length-(M+N-1) cyclic convolution.

- 2) a length-L FIR filtering can be computed by sectioning the infinite sequence into blocks of M numbers, then using an aperiodic convolution of a length-M sequence and a length-L one plus overlap-add. According to a), cyclic convolution applies too.

- 3) a length-L FIR filtering can be computed by sectioning the infinite sequence into overlapped blocks of N numbers with K overlapping ones (K<N), then using length-N cyclic convolution. This method is often called overlap-save.

In the first part, we deal with above all the FIR filtering algorithms. The filter's coefficients are taken as constant or fixed. However they can be extended to computing adaptive transversal filters [Duh89] in a fast way.

In the second part, our attention is mainly concentrated on the FIR filter architectures. However, the result in the Chapter 5 is applicable to a wider range of digital system design: multipliers, ALU of a general purpose processors and inner product computers, etc. The result in the Chapter 6 is also suitable for implementing inner product computers and adaptive transversal filters.

# Chapter 2

# A unified approach to the fast FIR filtering algorithms

FIR digital filters are widely used in digital signal filtering, and belong to the set of the most time consuming tasks in many systems. It is therefore of interest to derive efficient algorithms for computing FIR filtering. Many different approaches have been applied to solve this problem. Cyclic convolution based algorithms were first proposed [Sto66] soon after the rediscovery of fast Fourier transform algorithm (FFT). Aperiodic convolution algorithms were also applied to the FIR filtering [Aga74]. These algorithms are very efficient in terms of arithmetic complexity, and are therefore well suited for implementation on general purpose computers. A direct approach working directly on the FIR filtering equations was also proposed by Winograd [Win80]. All these algorithms are featured by the fact that arithmetic efficiency is obtained by working on large data blocks, and involve a global exchange of data inside this large vector.

The evolution of VLSI technology and the emergence of Digital Signal Processors have greatly boosted the real time signal processing. However, these kinds of implementations bring about some new constraints, and all the above algorithms are not always efficiently implemented through these new technologies because of their complex structure. For example, DSP's are highly optimized for implementing a multiply-accumulate operation. Therefore, all those "fast" algorithms were less efficient than the straightforward one when implemented on DSP's, except for very large filters or data blocks.

To overcome these problems, the authors proposed recently a new class of algorithms [Mou87]. Similar approaches were independently proposed at the same time by Vetterli [Vet88] and Kwan-Tsim [Kwa87].

At first glance, the new algorithms are quite different from the classical FIR filtering algorithms (large block convolution). Nevertheless, in

this paper we will show that all the above algorithms can be derived in a unified way and that this new approch provides all the intermediates between direct FIR computation and large block fast convolution algorithms, and between processing in time and in frequency, while opening some new possibilities.

Our objective is to unify all the main FIR filtering algorithms and to review the basic aspects of their derivation, in order to contribute to a better understanding to this problem, while providing some directions of the search for new algorithms.

The first step of the approach consists in a formulation of FIR filtering as a product of two polynomials (also used in [Mou87,Kwa87,Vet88]), which is then computed through the Chinese Remainder Theorem (CRT). Interpolating the polynomial product in different domains leads to different classes of algorithms while interpolating in different points leads to different algorithms in the same class. Thirdly this formulation is shown to lead to overlap-add algorithms. Transposition of the algorithms can result in all the overlap-save ones. We will show that the overlap-add and overlap-save techniques are essential to all kinds of algorithms, even to the FIR transversal filter itself. Since overlap-add and overlap-save schemes are the transpose of each other we show that they have the same arithmetic complexity.

# 2.1 Formulation of FIR filtering as a polynomial product

The FIR filtering is usually expressed as a convolution of two sequences: a finite sequence (hi) and an infinite one (xi). The result of the convolution is also an infinite sequence (yi). Their relation is as follows:

$$y_{n} = \sum_{i=0}^{L-1} x_{n-i} h_{i} \qquad n = 0, 1, 2, ..., \infty$$

(2.1)

It can be also written in the z-domain as a polynomial product of H(z) and X(z):

$$Y(z)=H(z)X(z)$$

(2.2)

H(z), X(z) and Y(z) are the z transform of  $\{hi\},\{xi\}$  and  $\{yi\}$  respectively. H(z) is a polynomial of finite degree (L-1) while the other two are of infinite degree.

By applying polyphase decomposition [Bel74] to each of the three terms in eq.(2), we get a polynomial product as follows:

$$Y_0 + Y_1 z^{-1} + \dots + Y_{N-1} z^{-N+1}$$

$$= (H_0 + H_1 z^{-1} + \dots + H_{N-1} z^{-N+1})(X_0 + X_1 z^{-1} + \dots + X_{N-1} z^{-N+1})$$

(2.3)

where {Hi}, {Xi} and {Yi} are polynomials in z-N:

$$H_j(z^N) = \sum_{m=0}^{L/N-1} h_{mN+j} z^{-mN}$$

$$Y_{i}(z^{N}) = \sum_{m=0}^{\infty} y_{mN+i} z^{-mN}$$

(2.4)

In fact,  $H(z^{-1})$ ,  $X(z^{-1})$  and  $Y(z^{-1})$  are each decimated into N interleaved sequences. The decimation rate N will be an important factor in our approach to construct fast FIR filtering algorithms. It represents the number of consecutive outputs to be computed together.

# 2.2 Fast computation of a polynomial product

The right side of eq.(2.3) is a product of two finite degree polynomials whose coefficients are themselves polynomials. The product has 2N-1 coefficients:

$$Q(z) = P_1(z) P_2(z)$$

$$= C_0 + C_1 z + ... + C_{N-1} z^{(N-1)} + ... + C_{2N-2} z^{(2N-2)}$$

(2.5)

where

$$P_1(z) = H_0 + H_1 z + ... + H_{N-1} z^{N-1}$$

$$P_2(z) = X_0 + X_1 z + ... + X_{N-1} z^{N-1}$$

(2.6)

Direct computation of {Ci} would require N<sup>2</sup> multiplications between {Hj} and {Xi}. Although such multiplications are in fact still FIR filterings, we take them first as usual multiplications. Nevertheless the application of the Chinese Remaider Theorem (CRT) is known to largely reduce the arithmetic

complexity. Using the CRT, Winograd has proved that (2N-1) multiplications are sufficient to compute  $\{Ci\}$ , instead of  $N^2$ . The theory of Winograd establishes the basis for fast algorithms.

Since the CRT plays an important role in fast algorithm derivation, let us first describe it.

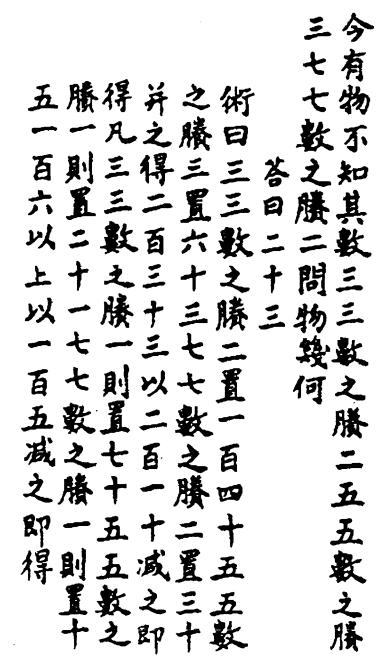

### 2.2.1 The Chinese Remainder Theorem

This theorem dates back to A.D.100 [Sod86]. Originally, it is a part of number theory. We are only interested in its extension to polynomial ring, since we discuss the polynomial product.

Chinese Remainder Theorem: Given a ring of polynomials modulo P(z) and

$$P(z) = \prod_{i=1}^{s} p_i(z)$$

$\{p_i(z)\}\$  are relatively prime, i.e.,  $p_i(z)$  has no common factors with  $p_j(z)$  when  $i\neq j$  for  $i,j\in\{1,2,...,s\}$ . Then for any polynomial Q(z), the following equation holds:

$$Q(z) \equiv \sum_{i=1}^{s} T_{i}(z)q_{i}(z) \mod P(z)$$

where

$$\begin{aligned} q_i(z) &\equiv Q(z) \bmod p_i(z) \\ T_i(z) &\equiv 1 \bmod p_i(z) \\ &\equiv 0 \bmod p_j(z) \quad \text{for} \quad j \neq i. \end{aligned}$$

The theorem states that, given only the residues  $\{q_i(z)\}$  of an unknown polynomial Q(z) in s distinct polynomial rings modulo  $p_i(z)$ , we can reconstruct Q(z) in the polynomial ring modulo P(z) from these residues. Q(z) will be unique if P(z) has higher order. The reconstructing polynomials  $\{T_i(z)\}$  depend only on  $\{p_i(z)\}$  and can be obtained by solving the following equation:

$$T_{i}(z) \equiv T'_{i}(z) \prod_{\substack{j=1\\j\neq i}}^{s} p_{j}(z) \equiv 1 \mod p_{i}(z)$$

# 2.2.2 Interpolation

The use of the CRT for computing a polynomial product is made mostly

by choosing:

$$p_i(z) = z - a_i;$$

i=0,1,...,2N-2 and  $a_i \neq a_j$  if  $j\neq i$  (2.7)

It is easy to evaluate:

$$P_1(a_i) \equiv P_1(z) \mod (z - a_i) = \sum_{k=0}^{M-1} H_k a_i^k$$

$$P_2(a_i) \equiv P_2(z) \mod (z - a_i) = \sum_{j=0}^{N-1} X_j a_i^j$$

(2.8)

## 2.2.3 Filtering

For obtaining the final result Q(z), we need to know the values  $Q(a_i)$  which is the residue  $q_i(z)$  of Q(z) modulo  $(z - a_i)$ . Since Q(z) is the product of  $P_1$  and  $P_2$ , we have

$$q_i(z)=Q(a_i)=P_1(a_i)P_2(a_i);$$

i=0,1,...,2N-2 (2.9)

Let us recall that  $P_1(a_i)$  and  $P_2(a_i)$  are the combinations of {Hj} and {Xi} respectively, while the latters are functions of z-N. Hence the above equations are still FIR filterings but at the sampling rate N times lower than the initial one.

Since the filter coefficients are constant, we can compute  $\{P_1(a_i), i = 0,1,...,2N-2\}$  before the filtering. This is one of the reasons that the computational load can be reduced, resulting in fast algorithms. This computation will not be taken into account in the subsequent evaluation of arithmetic complexity.

## 2.2.4 Reconstruction by the CRT

$\{Ti\}$  are precomputed, and when Pi(z) = z - ai, it turns out that their expression is fairly simple:

$$T_{i} = \prod_{\substack{j=0 \ j \neq i}}^{N+M-2} \frac{z-a_{j}}{a_{i}-a_{j}} = \frac{P(z)}{P(a_{i})(z-a_{i})}$$

(2.10)

and application of the CRT results in Q(z):

$$Q(z) = \sum_{i=0}^{N+M-2} Q(a_i) \prod_{\substack{j=0\\i\neq j}}^{N+M-2} \frac{z-a_j}{a_i-a_j} = P(z) \sum_{i=0}^{N+M-2} \frac{Q(a_i)}{P'(a_i)(z-a_i)}$$

(2.11)

which is very similar to the interpolation formulae of Lagrange. This is why {ai} are often referred as interpolation points.

# 2.3 Overlap

By comparing the left side and the right side in eq.(2.3) or (2.5), we get:

$$Y_{N-1} = C_{N-1}$$

$$Y_i = C_i + C_{i+N} z^{-N};$$

for  $i = 0,1,..., N-2$  (2.12)

We can observe that eq.(2.12) represents a procedure of overlap-add. All the  $\{Ci; i = 0,1,..., 2N-2\}$  are computed at one time and a block of N outputs  $\{Y_i\}$  is obtained by adding the terms  $\{C_{i+N}; i=0,1,...,N-1\}$  overlapping from the previous block. Till now we have accomplished all the steps for constructing an FIR filtering algorithm, as summarized below:

- 1) decimating H(z), X(z) and Y(z) at rate N to formulate the FIR filtering as an polynomial product;

- 2) interpolation of P<sub>1</sub> and P<sub>2</sub> at 2N-1 appropriate points a;

- 3) filtering like a dot product :  $Q(a_i) = P_1(a_i) P_2(a_i)$ , i = 0, 1,..., 2N-2;

- 4) reconstruction of Q(z) from its interpolated values  $Q(a_i)$ ;

- 5) overlap according to eq.(2.12).

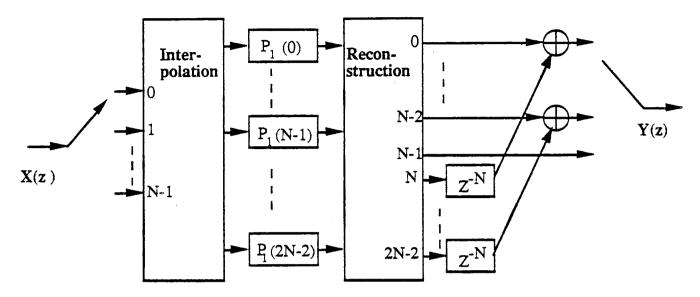

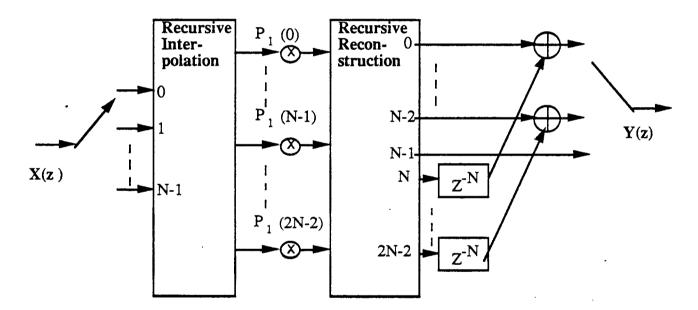

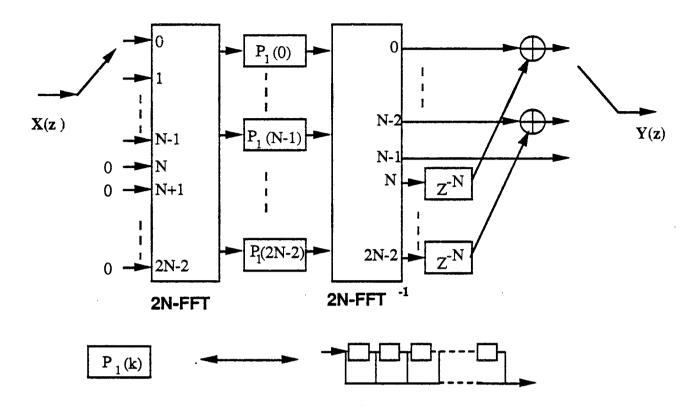

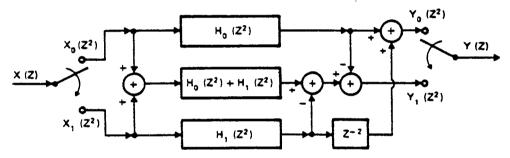

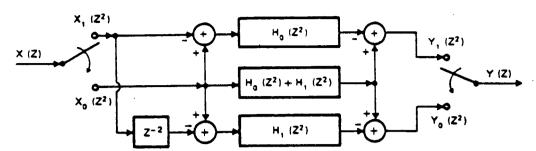

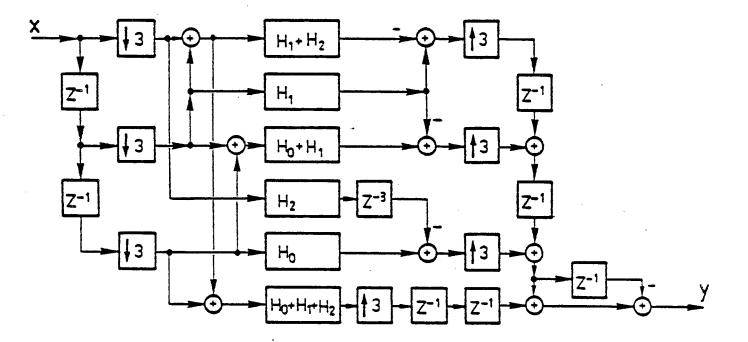

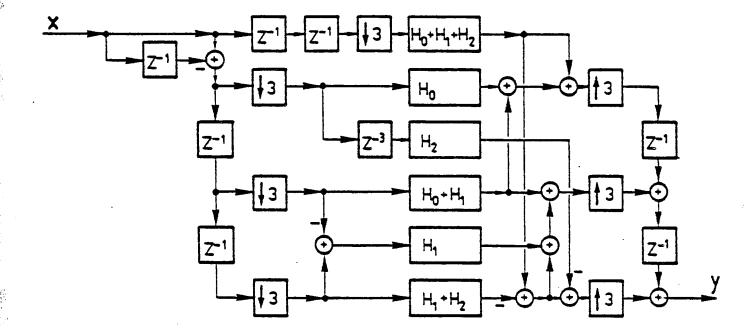

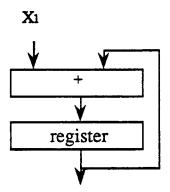

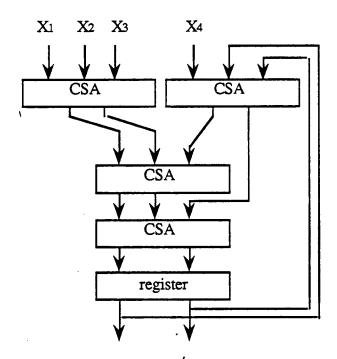

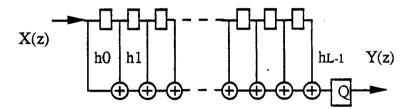

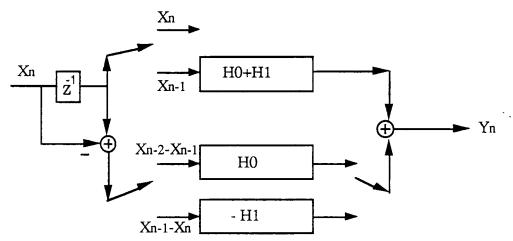

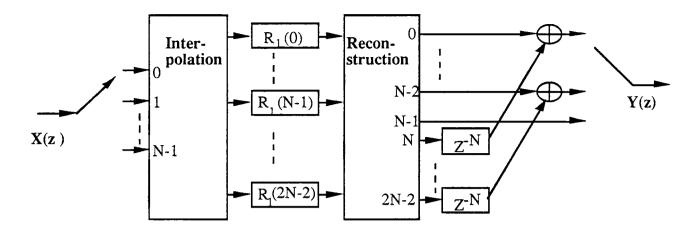

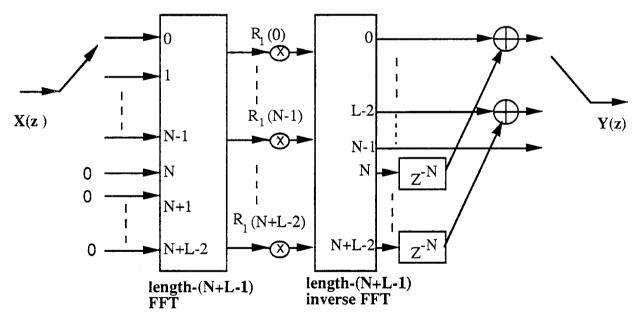

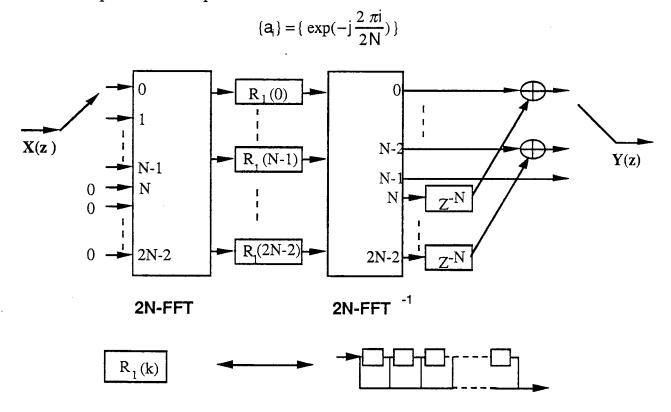

A general scheme is given in Fig.2.1. The above algorithm computes a block of N outputs.

The overlap differs the FIR filtering from other kinds of convolutions. It guarantees the continuity of computation and makes the filter running, while the cyclic convolution or the aperiodic convolution is a "local" computation.

It is well-known that a transversal FIR filter can be transposed. The transposed filter has the same transfer function. However the above

algorithms can be also transposed as will be shown in the following. This will lead to some connections between several types of algorithms.

Fig.2.1 General fast FIR filtering scheme

# 2.4 Pseudocyclic convolution

We denote in the following an algorithm computing  $N_1$  outputs of the filter and using  $N_2$  as decimating rate by  $F(N_1,N_2)$ . Although algorithms can be derived for  $N_1 \neq N_2$ , we will show in the Chapter 4 that they involve very complex structures and do not have any advantage over other algorithms. We will concentrate our investigation on the case where  $N_1 = N_2$ .

Considering eq.(2.3) and eq.(2.12) we may write the following equation:

$$\begin{bmatrix} Y_{N-1} \\ Y_{N-2} \\ \cdot \\ \cdot \\ \cdot \\ Y_{0} \end{bmatrix} = \begin{bmatrix} H_{0} & H_{1} & \cdots & H_{N-1} \\ z^{-N}H_{N-1} & H_{0} & \cdots & \ddots & \vdots \\ \cdot & \cdot & \cdot & \cdot & \cdot & \vdots \\ \cdot & \cdot & \cdot & \cdot & \cdot & H_{1} \\ z^{-N}H_{1} & \cdot & \cdot & z^{-N}H_{N-1} & H_{0} \end{bmatrix} \begin{bmatrix} X_{N-1} \\ X_{N-2} \\ \cdot & \vdots \\ X_{0} \end{bmatrix}$$

(2.13)

The right side is the product of a pseudocirculant matrix [Vai88] and a vector, or pseudocyclic convolution, which is in fact an F(N,N) system. In the context of pseudocircularity, we will show in the following the way to transpose an F(N,N) system and the way to obtain transposed version.

## 2.4.1 Diagonalization of a pseudocirculant matrix

In cyclic convolution, a fast algorithm diagonalizes a circulant matrix, the diagonalizing matrix is referred as rectangular transform [Aga76]. By analogy, a fast FIR filtering algorithm diagonalizes a pseudocirculant matrix. However the diagonalization here means a generalization of its conventional sense.

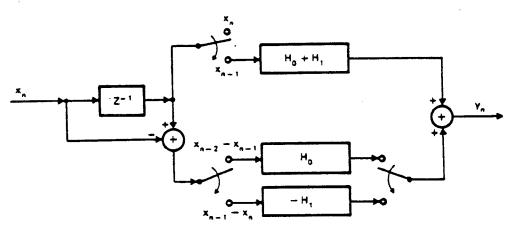

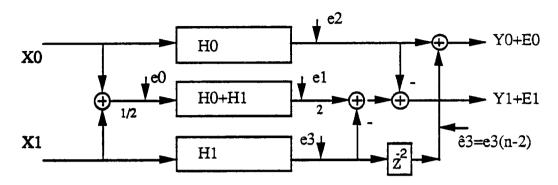

For example, a 2x2 pseudocirculant matrix can be diagonalized as follows [Kwa87,Vet88]:

$$\begin{bmatrix} h_0 & h_1 \\ z^{-2}h_1 & h_0 \end{bmatrix} = \begin{bmatrix} -1 & 1 & -1 \\ 1 & 0 & z^{-2} \end{bmatrix} \begin{bmatrix} h_0 \\ h_0 + h_1 \\ h_1 \end{bmatrix} \begin{bmatrix} 0 & 1 \\ 1 & 1 \\ 1 & 0 \end{bmatrix}$$

(2.14)

It is just the matrix representation of the algorithm presented in [Mou87]. In general an NxN pseudocirculant matrix can be diagonalized in to an MxM diagonal matrix with  $M\geq 2N-1$ . This lower bound is the natural result of Winograd's theory [Win80]. All the 'fast' algorithms have  $M< N^2$ .

We may also define a rectangular transform for the pseudocyclic convolution. There exists the term z-N in the transform matrix which recalls the continuity of computing. However most of the subsequent presentations employ other terminologies, in order to differ the FIR filtering algorithms from the cyclic convolution.

Vaidyanathan [Vai88] proposed a diagonalization of pseudocirculant by similarity transform, but this does not lead to fast algorithms, because the elements in the diagonal matrix are complex polynomials rather than simple numbers.

## 2.4.2 Transposition of an F(N,N) algorithm

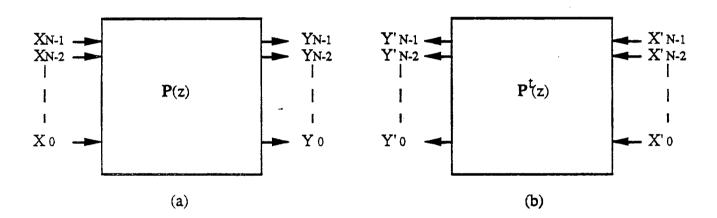

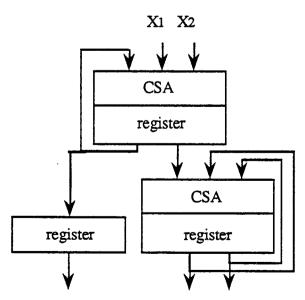

Let us consider an F(N,N) algorithm as an (N-input, N-output) system shown in Fig.2.2(a). Its transmission matrix is pseudocirculant:

$$\mathbf{P}(z) = \begin{bmatrix} H_0 & H_1 & \dots & H_{N-1} \\ z^{-N}H_{N-1} & H_0 & \dots & \dots & \dots \\ \vdots & \vdots & \ddots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \ddots & \vdots \\ z^{-N}H_1 & \dots & \vdots & z^{-N}H_{N-1} & H_0 \end{bmatrix}$$

(2.15)

The transposed system (shown in Fig.2.2(b)) will have  $P^t(z)$ , which is the transpose of P(z), as its transmission matrix according to Tellegen's Theorem for digital networks [Cro83].

Fig.2.2 (a) initial system; (b) transposed system.

Unlike (1-input, 1-output) systems, an (N-input, N-output) system's transpose will not perform the same function as the initial one unless P(z) is symmetric, i.e.,  $P(z) = P^t(z)$ . Owing to P's Toeplitz structure, we can manage to get the transposed system performing the same function as the initial one.

The transposed system is as follows:

$$\begin{bmatrix} Y'_{N-1} \\ Y'_{N-2} \\ \vdots \\ Y'_{0} \end{bmatrix} = \begin{bmatrix} H_{0} & z^{-N}H_{N-1} & \cdots & z^{-N}H_{1} \\ H_{1} & H_{0} & \cdots & \ddots \\ \vdots & \vdots & \ddots & \ddots \\ \vdots & \vdots & \ddots & \ddots \\ \vdots & \vdots & \ddots & \ddots \\ H_{N-1} & \cdots & \cdots & H_{1} & H_{0} \end{bmatrix} \begin{bmatrix} X'_{N-1} \\ X'_{N-2} \\ \vdots \\ X'_{0} \end{bmatrix}$$

$$(2.16)$$

If we permute the input elements  $\{X'_i\}$  and the output elements  $\{Y_i\}$  in such a way that their order is reversed, we will get the transposed system to perform the appropriate function:

$$\begin{bmatrix} Y'_{0} \\ Y'_{1} \\ \vdots \\ Y'_{N-1} \end{bmatrix} = \begin{bmatrix} H_{0} & H_{1} & \cdots & H_{N-1} \\ z^{-N}H_{N-1} & H_{0} & \cdots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \ddots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \ddots & \vdots \\ \vdots & \vdots & \ddots & \ddots & \vdots \\ z^{-N}H_{1} & \cdots & z^{-N}H_{N-1} & H_{0} \end{bmatrix} \begin{bmatrix} X'_{0} \\ X'_{1} \\ \vdots \\ X'_{N-1} \end{bmatrix}$$

$$(2.17)$$

The above demonstration is general, so that all (N-input,N-output) systems whose transmission matrix is Toeplitz can be transposed to perform the same function as the initial system after permuting the inputs and outputs in a reversed order. Thus, it can be applied to all kinds of convolution systems. Winograd has already proposed to transpose circular convolution algorithms in the same manner [Win80]. We summarize this principle as the following theorem.

Theorem: Having Toeplitz transmission matrix is sufficient for an (N-input, N-output) system to be transposed and to perform the same function after permuting the inputs and outputs in a reversed order.

Hence, we can transpose an F(N,N) algorithm in a rather easy way. In fact, a fast F(N,N) algorithm diagonalizes a pseudocirculant matrix:

$$\mathbf{P}(\mathbf{z}) = \mathbf{A}_{\mathbf{N}\mathbf{x}\mathbf{M}} \, \mathbf{B}_{\mathbf{M}\mathbf{x}\mathbf{M}} \, \mathbf{B}_{\mathbf{M}\mathbf{x}\mathbf{N}} \tag{2.18}$$

where  $\mathbf{H}_{MxM}$  is a diagonal matrix. Then the transposition of  $\mathbf{P}(z)$  is

$$\mathbf{P}^{t}(z) = \mathbf{B}^{t} \mathbf{H} \mathbf{A}^{t} \tag{2.19}$$

Permuting the inputs and outputs in a reversed order is equivalent to multiply J= antidiag(1,1,...,1). Then the following equation holds:

$$\mathbf{P}(\mathbf{z}) = (\mathbf{J}\mathbf{B}^{\mathsf{t}}) \mathbf{H} (\mathbf{A}^{\mathsf{t}}\mathbf{J}) \tag{2.20}$$

Therefore, we get the transposed version of (2.18). The new pair of diagonalizing matrix is  $(\mathbf{JB}^t)$  and  $(\mathbf{A}^t\mathbf{J})$ .

Let us consider as an example an F(2,2) algorithm, as given in (2.14). It is expressed in matrix form as:

$$\begin{bmatrix} \mathbf{y}_{1} \\ \mathbf{y}_{0} \end{bmatrix} = \begin{bmatrix} \mathbf{h}_{0} & \mathbf{h}_{1} \\ \mathbf{z}^{-2} \mathbf{h}_{1} & \mathbf{h}_{0} \end{bmatrix} \begin{bmatrix} \mathbf{x}_{1} \\ \mathbf{x}_{0} \end{bmatrix} \\

= \begin{bmatrix} -1 & 1 & -1 \\ 1 & 0 & \mathbf{z}^{-2} \end{bmatrix} \begin{bmatrix} \mathbf{h}_{0} & \mathbf{h}_{0} + \mathbf{h}_{1} \\ \mathbf{h}_{1} \end{bmatrix} \begin{bmatrix} 0 & 1 \\ 1 & 1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} \mathbf{x}_{1} \\ \mathbf{x}_{0} \end{bmatrix} \tag{2.21}$$

therefore

$$\mathbf{A} = \begin{bmatrix} -1 & 1 & -1 \\ 1 & 0 & z^{-2} \end{bmatrix} \qquad \mathbf{B} = \begin{bmatrix} 0 & 1 \\ 1 & 1 \\ 1 & 0 \end{bmatrix}$$

Following (2.20), we obtain the transposed version of (2.21):

$$\begin{bmatrix} \mathbf{y}_{1} \\ \mathbf{y}_{0} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \end{bmatrix} \begin{bmatrix} \mathbf{h}_{0} \\ & \mathbf{h}_{0} + \mathbf{h}_{1} \\ & & \mathbf{h}_{1} \end{bmatrix} \begin{bmatrix} 1 & -1 \\ 0 & 1 \\ \mathbf{z}^{-2} & -1 \end{bmatrix} \begin{bmatrix} \mathbf{x}_{1} \\ \mathbf{x}_{0} \end{bmatrix}$$

(2.22)

## 2.4.3 Identical arithmetic complexity in direct and transposed forms

It is clear, following the above explanations, that the multiplicative complexity is not changed by transposition. Let us consider the additive complexity in an (N-input,N-output) system.

A digital network is composed of only branches and nodes. There are two kinds of nodes: a (M,1) summing node that adds M inputs into 1 output, and a (1,M) branching node that branches 1 input into M outputs. A (M,1) summing node can be split into M-1 (2,1) summing nodes. A (1,M) branching node can be also split into M-1 (1,2) branching nodes. Then it is easy to transform the network to an equivalent one having only (2,1) summing nodes and (1,2) branching nodes. After transposition, the summing nodes become branching nodes and vice versa.

The number of additions in the initial network is equal to that of (2,1) summing nodes, denoted by Ns. The number of additions in the transposed network is equal to that of (2,1) branching nodes in the initial network, denoted by Nb. The additive complexity in initial and transposed algorithms is identical if and only if Ns=Nb, and we show in the following that this property holds for (N-input, N-output) systems.

**Proof**: For an (N-input,N-output) network, if we connect the N inputs to the N outputs graphically, we get a closed network where every branch coming out from a node should enter into another node. Then the number of outputs of all nodes is equal to that of inputs of all nodes. A (2,1) summing node has two inputs and one output while a (1,2) branching node has one input and two outputs. We get:

Nb+2Ns=2Nb+Ns

Ns=Nb

end of proof.

## 2.5 Remarks

A general approach to derive fast FIR filtering algorithms has been described. Some parameters such as decimating rate N and interpolation points are not defined. We will show in the next chapter how the choice of these parameters affects the resulting algorithm. In fact all the classical algorithms choose N tacitly greater than the filter's length. However it is also feasible using smaller N to derive algorithms of interest.

The pseudocyclic convolution is a good representation of the FIR filtering process. Several properties, such as transposability of an F(N,N) algorithm, equality of arithmetic complexity in direct and transposed form, have been proved under the representation.

# Chapter 3

# Review on the FIR filtering algorithms and new possibilities

In this chapter we will show that the classical algorithms are shown to be special cases of the approach presented in the previous chapter. These algorithms include three typical ones: FFT-based algorithms proposed by Stockham [Sto66]; Algorithms using aperiodic convolutions proposed by Agarwal and Burrus [Aga74]; Winograd algorithms [Win80].

Some new possibilties are also investigated. First the recently proposed algorithms [Mou87,Kwa87,Vet88], termed short length FIR filtering algorithms (SLFIR), are briefly described. A comprehensive study on this class of algorithms is in the next chapter. Secondly we present shorter FFT-based algorithms while in the frequency domain either real or complex FIR filterings are performed. This class of algorithms represents all the intermediate ones between processing in time and in frequency. Short length complex FIR filtering algorithms(SLCFIR) will also be derived using the approach.

It is a general belief that when the filter's length L is large, classical FFT-based scheme will outperform all the other algorithms. However the combination of short length real and complex FIR filtering algorithms and the shorter FFT-based schemes results in an algorithm requiring even less arithmetic operations than the classical ones as far as L≥4.

# 3.1 Review on the classical algorithms

The "fast" (in the sense of reducing arithmetic complexity) computation of FIR filtering through FFT and its inverse was soon recognized to be speed-efficient on general-purpose computers [Sto66] after the rediscovery of FFT. High speed convolvers based on FFT's were also built in hardware.

Nevertheless, the FFT-based FIR filtering implies to work on large overlapping signal block, thus resulting in heavy hardware requirement. Furthermore, since most Digital Signal Processor (DSP's) are optimized for a multiply-accumulate structure, transform-based FIR filtering is of no practical interest on DSP's.

There were the motivations for the proposal of a new class of algorithms [Mou87], reducing the arithmetic complexity but retaining the multiply-accumulate structure.

However the above two classes of algorithms have quite different presentations. Nevertheless, we will show in the following that they are just special cases of the general scheme in Fig.2.1.

## 3.1.1 FFT-based algorithms

Let us choose  $N \ge L$ , then

Hi

$$(z^{-N}) = hi$$

$0 \le i \le L-1$

= 0  $L \le i \le N-1$  (3.1)

Replacing (Hi) in eq.(2.6) by the the above terms, we get:

$$P_1(z) = h_0 + h_1 z + h_2 z^2 + \dots + h_{L-1} z^{L-1}$$

(3.2)

$P_2(z)$  remains unchanged as in (2.6). Since the polynomial  $P_1$  is now of degree L-1 and L $\leq$ N, the minimum number of necessary interpolation points is N+L-1 instead of 2N-1. If we choose  $K(\geq N+L-1)$  points on the unit circle  $\{\exp(-2\pi i/K); i = 0,1,..., K-1\}$  as interpolation points, then

$$P_{1}(a_{i}) = \sum_{k=0}^{L-1} h_{k} W^{ik}$$

$$P_{2}(a_{i}) = \sum_{k=0}^{N-1} X_{k} W^{ik}$$

(3.3)

$\{P_1(ai); i = 0,1,...,K-1\}$  is the length-K DFT of  $\{hi ; i = 0,1,...,L-1\}$  so that FFT's applies for the computation of the interpolation values. Likewise,  $\{P_2(ai); i = 0,1,...,L-1\}$

0,1,...,K-1 is the length-K DFT of  $\{Xi; i = 0,1,...,N-1\}$ . After the pointwise multiplications  $P_1(ai)P_2(ai) = Q(ai)$ , we can show:

$$Q(z) = \sum_{i=0}^{N+L-2} Q(a_i) \sum_{j=0}^{N+L-2} \frac{1}{N} W^{-ij} z^j$$

(3.4)

The coefficients of Q(z) is exactly the inverse DFT of  $\{Q(ai)\}$ :

$$C_{j} = \frac{1}{N} \sum_{i=0}^{N+L-2} Q(a_{i}) W^{-ij}$$

(3.5)

The overlap-add technique is then applied to get the correct filter outputs. Fig.3.1 depicts the general scheme for all the FFT-based algorithms.  $\{P_1(ai)\}$  can be precomputed. Its computation will not be counted in the subsequent evaluation of arithmetic complexity.

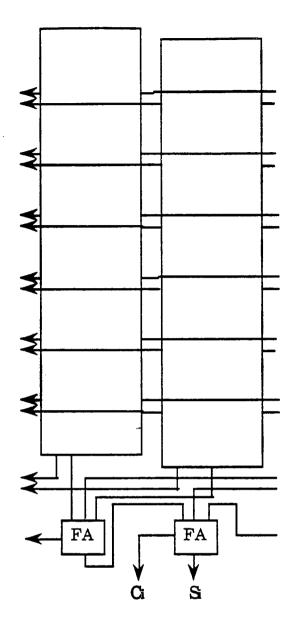

Fig.3.1 FFT-based overlap-add FIR filtering scheme

Due to the complex interpolation points all the computations have to be performed in the complex domain. When the data is real, we can apply the real-valued FFT algorithms to remove the redundancy that appears in the computation [Duh87,Sor87].

Let us take a simple example of computing a length- $2^m$  filter, usually we choose  $N=L=2^m$  so that a length-2L DFT's and its inverse can be used to compute the N outputs together. Then K should be  $2L(=2^{m+1})$  instead of 2L-1, since a length-2L DFT's is much more easier to implement than a length-(2L-1) one. Suppose we use the split-radix FFT and eliminate unnecessary additions on input and on output. The resulting arithmetic complexity is:

IIIa) length-2<sup>m</sup> real filter (per 2<sup>m</sup> outputs):

$$M_r = 2^m (2m-1)+3$$

$A_r = 2^m (6m-2)+3$

the arithmetic complexity per output is:

$$m_r = 2m-1+3 \cdot 2^{-m}$$

$a_r = 6m-2+3 \cdot 2^{-m}$

$m_r + a_r = 8m \cdot 3+6 \cdot 2^{-m}$

A 3-real-multiplication-and-3-real-addition [Nus82] algorithm is used for the complex number multiplication for the above evaluation of arithmetic complexity.

There is a slight difference in arithmetic complexity between the above scheme and a length-2<sup>m+1</sup> cyclic convolution:

$$\begin{aligned} \mathbf{M_r} &= \mathbf{M_{cc}}(2^{m+1} \ ) \\ \mathbf{A_r} &= \mathbf{A_{cc}}(2^{m+1} \ ) - 2^m - 2 \end{aligned}$$

The difference is due to the fact that the input block of length  $2^m$  is padded with  $2^m$  zeroes.

# 3.1.2 Algorithms using aperiodic convolutions

Agarwal and Burrus [Aga74] presented a class of algorithms using small radix aperiodic convolution (AC) algorithms to compute recursively a long polynomial product and then overlapping.

A radix-2 fast aperiodic convolution algorithm can be derived by the CRT using  $\{0,1,\infty\}$  as interpolation points:

$$(x_0 + x_1 z)(h_0 + h_1 z)$$

$$= x_0 h_0 + [(x_0 + x_1)(h_0 + h_1) - x_0 h_0 - x_1 h_1]z + x_1 h_1 z^2$$

(3.6)

Only 3 multiplications are required instead of 4.

We will show how to use the above algorithm to derive FIR filtering algorithms.

Let the decimating rate N=L (the length of the filter, assumed even). The filtering equation becomes:

$$Y_0 + Y_1 z + ... + Y_{L-1} z^{L-1}$$

$$= (h_0 + h_1 z + ... + h_{L-1} z^{L-1}) (X_0 + X_1 z + ... + X_{L-1} z^{L-1})$$

(3.7)

A reorganization of the above equation leads to:

$$(Y_0 + Y_1 z + ... + Y_{L/2-1} z^{L/2-1}) + z^{L/2} (Y_{L/2} + ... + Y_{L-1} z^{L/2-1})$$

$$= [(h_0 + h_1 z + ... + h_{L/2-1} z^{L/2-1}) + z^{L/2} (h_{L/2} + ... + h_{L-1} z^{L/2-1})] \times$$

$$[(X_0 + X_1 z + ... + X_{L/2-1} z^{L/2-1}) + z^{L/2} (X_{L/2} + ... + X_{L-1} z^{L/2-1})]$$

$$(3.8)$$

or

$$E0 + E1z^{L/2} = (G0 + G1z^{L/2}) (F0 + F1z^{L/2})$$

with

$$\begin{split} & \text{E0} = \text{Y}_0 + \text{Y}_1 \text{z} + \ldots + \text{Y}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \\ & \text{G0} = \text{h}_0 + \text{h}_1 \text{z} + \ldots + \text{h}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \\ & \text{F0} = \text{X}_0 + \text{X}_1 \text{z} + \ldots + \text{X}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \end{split} \qquad \begin{aligned} & \text{E1} = \text{Y}_{\text{L}/2} + \text{Y}_{\text{L}/2+1} \text{z} + \ldots + \text{Y}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \\ & \text{G1} = \text{h}_{\text{L}/2} + \text{h}_{\text{L}/2+1} \text{z} + \ldots + \text{h}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \\ & \text{F1} = \text{X}_{\text{L}/2} + \text{X}_{\text{L}/2+1} \text{z} + \ldots + \text{X}_{\text{L}/2-1} \text{z}^{\text{L}/2-1} \end{aligned}$$

Such formulation allows us to apply the radix-2 AC algorithm, resulting in:

$$E0 + E1z^{L/2}$$

= G0F0+ [(G0+ G1) (F0+F1) - G0F0- G1F1]  $z^{L/2}$  + G1F1 $z^{L}$  (3.9)

By overlapping, we get:

$$E0 = G0F0 + G1F1z^{L}$$

$E1 = (G0 + G1)(F0 + F1) - G0F0 - G1F1$  (3.10)

About 25% reduction can be achieved in the number of arithmetic operations. This gain is obtained by removing the redundancy existing between computing two groups of outputs:{Y0,Y1,...,YL/2-1} and {YL/2,...,YL-1}.

Since G0F0, (G0+G1)(F0+F1), G1F1 are themselves aperiodic convolutions, we can once more apply the radix-2 AC algorithm to them before overlapping. This is equivalent to a recursive interpolation using the same interpolating points. Further gain in arithmetic complexity can be obatined by removing the redundancy in computing four groups of outputs: {Y0,Y1,...,YL/4-1}, {YL/4,...,YL/2-1}, {YL/2,...,Y3L/4-1} and {Y3L/4,...,YL-1}. Evidently this procedure can be recursively applied, resulting in further reduction in arithmetic complexity. Agarwal and Burrus presented this technique using multidimensional formulation [Aga74].

For L=2<sup>m</sup>, a thorough recursion using the radix-2 algorithm results in an fast algorithm requiring 3<sup>m</sup> multiplicatons, instead of 4<sup>m</sup> by direct computation. The additive complexity is evaluated in [Nus82]. Otherwise (L-1) additions are necessary for overlapping to establish an FIR filtering algorithm. The arithmetic complexity of the filtering algorithms thus constructed is given in Table.3.1.

Table.3.1 Arithmetic complexity of Agarwal&Burrus filtering algorithms (per N outputs).

| N   | M    | A     |

|-----|------|-------|

| 2   | 3    | 4     |

| 4   | 9    | 22    |

| 8   | 27   | 88    |

| 16  | 81   | 310   |

| 64  | 729  | 3262  |

| 128 | 2187 | 10168 |

| 256 | 6561 | 31271 |

|     |      |       |

The above formulation of a long aperiodic convolution as a radix-2 one is rather decimation-in-frequency, by analogy of the terms for defining FFT's. It is also feasible to derive a decimation-in-time algorithm by the following formulation:

$$(Y_0 + Y_2 z^2 + ... + Y_{L/2-1} z^{L-2}) + z (Y_1 + ... + Y_{L-1} z^{L-2})$$

$$= [(h_0 + h_2 z^2 + ... + h_{L/2-1} z^{L-2}) + z (h_1 + ... + h_{L-1} z^{L-2})] \times$$

$$[(X_0 + X_2 z^2 + ... + X_{L/2-1} z^{L-2}) + z (X_1 + ... + X_{L-1} z^{L-2})]$$

$$(3.11)$$

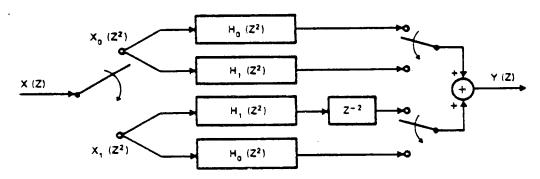

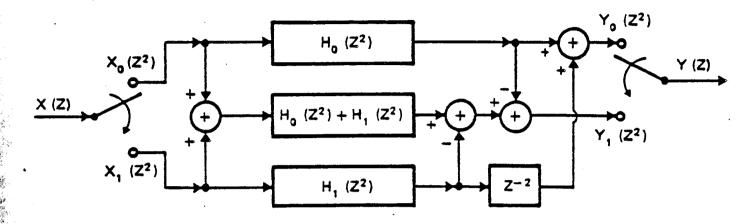

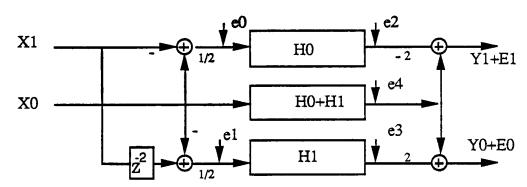

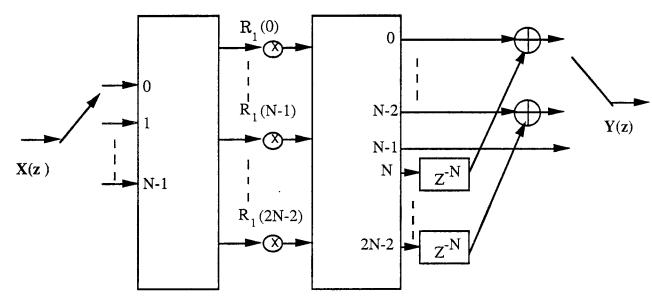

The radix-2 AC algorithm is then applicable to the above equation. Further recursion results in an algorithm with the same arithmetic complexity as before. A general scheme is given in Fig.3.2 for small-radix aperiodic convolution based FIR filtering algorithms.

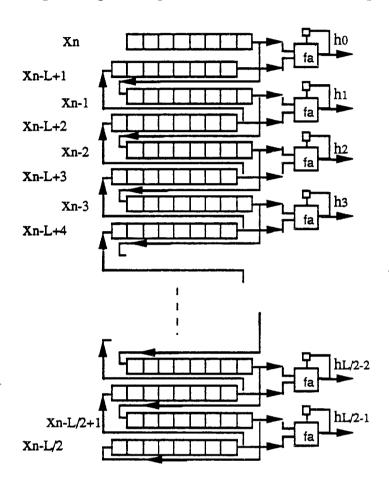

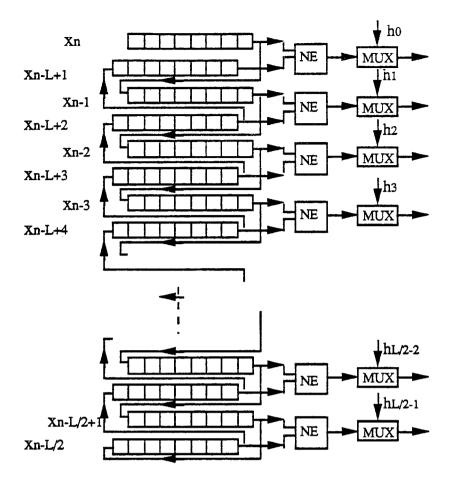

Fig.3.2 Fast FIR filtering scheme by Agarwal&Burrus technique

This kind of algorithms is often preferable for computing small or medium size FIR filters as well as for full precision implementation[Aga74].

## 3.1.3 Winograd algorithms

Winograd's theory [Win80] on the arithmetic complexity of computation is a milestone for fast FIR filtering algorithms as well as for FFT and polynomial product algorithms. He proposed an original class of FIR filtering

algorithms and provided the lower bound on the number of multiplications for computing an FIR filter.

It is intended by Winograd to compute the FIR filtering under the presentation below:

$$\begin{bmatrix} y_{n} \\ y_{n-1} \\ \vdots \\ y_{n-L+1} \end{bmatrix} = \begin{bmatrix} x_{n-L+1} & \cdots & x_{n-1} & x_{n} \\ x_{n-L} & x_{n-L+1} & \cdots & x_{n-1} \\ \vdots & \vdots & \ddots & \vdots \\ x_{n-2L+2} & \cdots & x_{n-L} & x_{n-L+1} \end{bmatrix} \begin{bmatrix} h_{L-1} \\ h_{L-2} \\ \vdots \\ h_{0} \end{bmatrix}$$

$$(3.12)$$

It is tacitly assumed to compute L outputs together, given L the filter's length.

First of all, a small radix aperiodic convolution algorithm, for example the one in eq.(3.6), is transposed to compute the following operation in a fast way [Win80]:

$$\begin{bmatrix} y_{n} \\ y_{n-1} \end{bmatrix} = \begin{bmatrix} x_{n-1} & x_{n} \\ x_{n-2} & x_{n-1} \end{bmatrix} \begin{bmatrix} h_{1} \\ h_{0} \end{bmatrix} = \begin{bmatrix} x_{n-1} & (h_{1} + h_{0}) - (x_{n-1} - x_{n}) & h_{0} \\ x_{n-1} & (h_{1} + h_{0}) + (x_{n-2} - x_{n-1}) & h_{1} \end{bmatrix}$$

(3.13)

This is an algorithm computing 2 outputs of a length-2 FIR filter with only 3 multiplications. Eq.(3.12) can be formulated in block form:

$$\begin{bmatrix} E_1 \\ E_0 \end{bmatrix} = \begin{bmatrix} F_0 & F_1 \\ F_2 & F_0 \end{bmatrix} \begin{bmatrix} G_1 \\ G_0 \end{bmatrix}$$

(3.14)

with

$$E1 = \begin{bmatrix} y_{n} \\ y_{n-1} \\ \vdots \\ y_{n-L/2+1} \end{bmatrix} \qquad E0 = \begin{bmatrix} y_{n-L/2} \\ y_{n-L/2-1} \\ \vdots \\ y_{n-L+1} \end{bmatrix} \qquad G1 = \begin{bmatrix} h_{L-1} \\ h_{L-2} \\ \vdots \\ h_{L/2} \end{bmatrix} \qquad G0 = \begin{bmatrix} h_{L/2-1} \\ h_{L/2-2} \\ \vdots \\ h_{0} \end{bmatrix}$$

Then (3.13) applies to the above computation for reduction of arithmetic complexity:

$$\begin{bmatrix} E_1 \\ E_0 \end{bmatrix} = \begin{bmatrix} F_0 (G_1 + G_0) - (F_0 - F_1) G_0 \\ F_0 (G_1 + G_0) + (F_2 - F_0) G_1 \end{bmatrix}$$

(3.15)

Further iteration of the algorithm in (3.13) is feasible in computing F0(G1+G0), (F0-F1)G0, (F2-F0)G1. For L=2<sup>m</sup>, a thorough iteration results in 3<sup>m</sup> multiplications. The arithmetic complexity for certain lengths is listed in Table.3.2.

Since eq.(3.13) is just the transpose of the radix-2 AC algorithm in (3.6), the recursive application of (3.13) is the transpose of that of (3.6). Hence we can conclude that Winograd algorithms are the transpose of those of Agarwal and Burrus.

We have proved in last chapter that both the direct and transposed forms of an FIR filtering algorithm have the same complexity. But Table.3.2

and 3.1 show different number of additions. The reason for such difference is that Winograd has taken into account the redundancy due to computing two successive blocks of outputs while Agarwal and Burrus were not concerned with the overlap.

Table.3.2 Arithmetic complexity of Winograd filtering algorithms (per N outputs).

| N   | M          | A           |

|-----|------------|-------------|

| 2   | 3          | 4           |

| 4   | 9          | 20          |

| 8   | <b>2</b> 7 | <b>7</b> 6  |

| 16  | 81         | <b>26</b> 0 |

| 64  | 729        | 2660        |

| 128 | 2187       | 8236        |

| 256 | 6561       | 25220       |

For example in case L=4, we have

$$F0 - F1 = \begin{bmatrix} x_{n-3} - x_{n-1} & x_{n-2} - x_n \\ x_{n-4} - x_{n-2} & x_{n-3} - x_{n-1} \end{bmatrix}$$

$$F2 - F0 = \begin{bmatrix} x_{n-5} - x_{n-3} & x_{n-4} - x_{n-2} \\ x_{n-6} - x_{n-4} & x_{n-5} - x_{n-3} \end{bmatrix}$$

(3.16)

(3.16)

Between (F0-F1) and (F2-F0), there is a common addition  $(x_{n-4}$  -  $x_{n-2})$  so that one addition can be saved. Realizing that  $(x_{n-6} - x_{n-4})$  is already computed for last 4 outputs, we can save one more addition. Hence in case L=4 Winograd algorithm requires 2 less additions than Agarwal&Burrus algorithm does as shown in Table.3.1 and 3.2. We may also remove the 2 extra additions in the latter algorithm but it is less systematic than in the Winograd algorithm.

# 3.2 Short length FIR filtering algorithms

Let N = 2. If we choose  $\{0,1,\infty\}$  as interpolation points, then

$$\begin{split} P_1(a_0) &= H_0(z^2) & P_2(a_0) = X_0(z^2) \\ P_1(a_1) &= H_0(z^2) + H_1(z^2) & P_2(a_1) = X_0(z^2) + X_1(z^2) \\ P_1(a_2) &= H_1(z^2) & P_2(a_2) = X_1(z^2) \end{split} \tag{3.17}$$

Application of the procedure stated in the last chapter leads to the following algorithm:

$$Y_0(z^2) = P_1(a_0) P_2(a_0) + z^{-2} P_1(a_2) P_2(a_2)$$

$$Y_1(z^2) = P_1(a_1) P_2(a_1) - P_1(a_0) P_2(a_0) - P_1(a_2) P_2(a_2)$$

(3.18)

Different authors have presented this result in their own way [Kwa87,Mou87,Vet88]. Of course further decompositions are still feasible, together with higher radix or mixed radix decomposition.

There are four simplest interpolation points in real number domain  $\{0,1,-1,\infty\}$ . The other variants can be obtained by using interpolation point sets like  $\{0,-1,\infty\}$ ,  $\{0,1,-1\}$  or  $\{1,-1,\infty\}$ . Although interpolation points other than  $\{0,1,-1,\infty\}$  can be used, they will lead to much more complicated algorithms and become out of practical interest. A study of real FIR filtering algorithms with small N can be found in the next chapter.

# 3.3 Shorter FFT-based algorithms

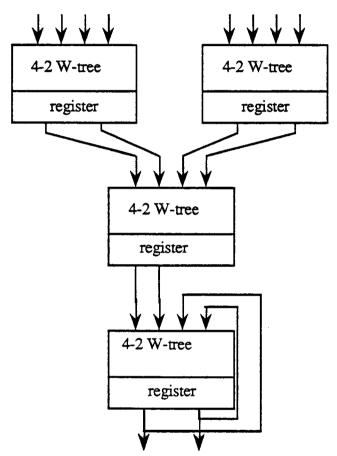

We present two new schemes in this section as results of the approach: one is based on shorter FFT's (length of FFT < length of the filter), the other is fast short length complex FIR filtering algorithms. We will show also that combining the two schemes may result in less arithmetic operations than conventional ones as mentioned in the last section.

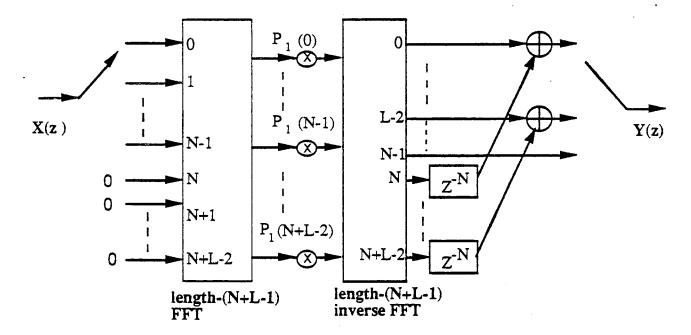

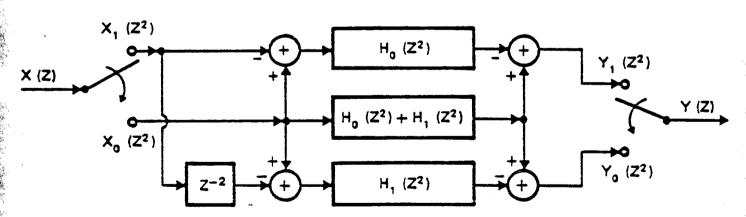

We have shown that when N is large, the terms  $\{P_1(ai)\ P_2(a_i);\ a_i = \exp(-2\pi i/K)\}$  are the products of two complex numbers. Now if we choose a relatively small N (<L), the  $H_i(z^N)$  are no longer constants but higher degree polynomials and the terms  $P_1(ai)P_2(ai)$  become length-L/N either complex or real FIR filtering. The general framework of algorithm will be a length-(2N-1) DFT's plus 2N-1 complex FIR filters and then a length-(2N-1) inverse DFT's. Overlapadd is performed at the last step. Nevertheless a length-2N FFT transformer is simpler and thus is prefered [Kwa87,Mou88]. An alternate scheme is the

transposed version, i.e., the overlap-save scheme as depicted in Fig.3.3. When the data are real, further improvement can be brought about by applying the fast cyclic convolution algorithm for real data [Duh87,Sor87] to the computation of the polynomial product.

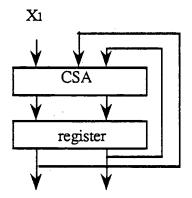

Fig.3.3 Shorter FFT-based FIR filtering scheme

In Fig.3.3, the FFT and FFT <sup>-1</sup> are used to perform the polynomial product, the remaining task is to compute the complex filters between FFT and FFT <sup>-1</sup>.

Let us restudy the case of computing a filter of length- $2^m$  for the sake of comparison. Now we choose  $N=L/2=2^{m-1}$ . Then according to eq.(2.4) we have

$$H_i = h_i + h_{i+L/2}z^{-L/2}; \quad i = 0,1,...,L/2-1$$

(3.19)

Using  $\{a_i = W^i = \exp(-2\pi i/2N) = \exp(-2\pi i/L); i=0,1,...L-1\}$  as interpolation points, we obtain a scheme based on length-L FFT and its inverse, instead of length-2L one. we derive explicitely the length-2 complex FIR filters in the frequency domain:

$$P_{1}(W^{i}) = \frac{1}{L} \sum_{j=0}^{L/2-1} H_{j}W^{ij}$$

$$= (\frac{1}{L} \sum_{j=0}^{L/2-1} h_{j}W^{ij}) + (\frac{1}{L} \sum_{j=0}^{L/2-1} h_{j+L/2}W^{ij}) z^{-L/2} \qquad i = 0, 1,..., L-1$$

(3.20)

The scaling coefficient 1/L is due to the inverse FFT in the scheme. By incorporating 1/L into the complex FIR filters, L multiplications are avoided and the scaling is naturally performed. Since N=L/2, 2<sup>m-1</sup> outputs are computed. The resulting arithmetic complexity is:

IIIb) length- $2^m$  real filter (per  $2^{m-1}$  outputs):

$$M_r = 2^m m + 2$$

$A_r = 2^{m-1} (6m - 5) + 1$

the arithmetic complexity per output is:

$$m_r = 2m + 2 \cdot 2^{-m+1}$$

$a_r = 6m \cdot 5 + 2 \cdot 2^{-m+1}$

$m_r + a_r = 8m \cdot 5 + 8 \cdot 2^{-m}$

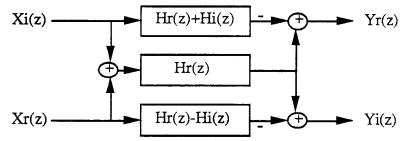

Taking into account the symmetry of the Fourier transform of real signal, we have used in the frequency domain only two length-2 real FIR filters and N/2-1 (=  $2^{m-1}$ -1) length-2 complex FIR filters. The fast computation of complex FIR filtering is similar to the fast complex number multiplication algorithm with 3 real multiplications and 3 real additions. This can be shown as follows. Complex FIR filtering is described as:

$$Yr(z)+jYi(z) = [Hr(z)+jHi(z)][Xr(z)+jXi(z)]$$

(3.21)

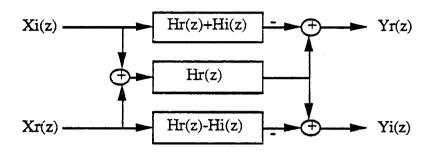

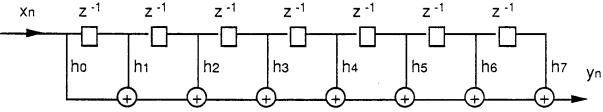

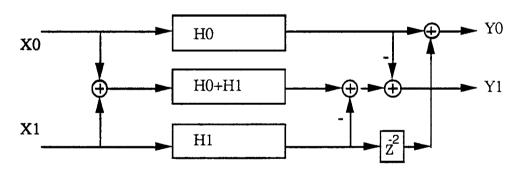

By applying the fast complex number multiplication algorithm, we obtain the following complex FIR filtering algorithm:

$$Yr(z) = Hr(z) [Xr(z)+Xi(z)] - [Hr(z)+Hi(z)] Xi(z)$$

$Yi(z) = Hr(z) [Xr(z)+Xi(z)] - [Hr(z)-Hi(z)] Xr(z)$  (3.22)

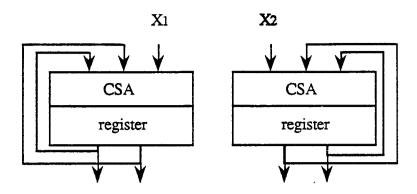

Fig.3.4 depicts the fast complex FIR filtering scheme. Note that (Xr+Xi) needs only one addition per output, since all the terms computed for the previous outputs can be stored and used for the present output. For a length-L complex FIR filter only 3L real multiplications and 3L real additions are required per complex output datum. Then (6 mults, 6 adds) are used to compute each of the length-2 complex FIR filters.

Fig.3.4 Complex FIR filtering using three real FIR filters

Comparing a) with b), we find that the new scheme requires more multiplications and less additions. Furthermore the sum of computational operations per output is reduced. In certain computers, a multiplication and an addition require almost the same computing time. The new scheme may be very competitive with the conventional one. It is also competitive in other computers since the difference of arithmetic complexity between the two schemes is very small. An important difference is that the conventional scheme needs length-2L DFT's while the new scheme uses only length-L DFT's. In general, smaller length DFT's can be more efficiently implemented. This is another advantage of the new scheme. Since the block length is proportional to the delay in processing, the system delay is also halved, a fact of interest for real time processing.

We can also choose N=L/4 and  $\{ai\}=\{exp(-4\pi i/L);\ i=0,1,...,L/2-1\}$ . This results in a scheme with length-L/2 DFT's and length-4 FIR filters in the frequency domain. The arithmetic complexity is as follows:

IIIc) length-2<sup>m</sup> real filter (per 2<sup>m-2</sup> outputs):

$$M_r = 2^{m-2} (2m+4)$$

$$A_r = 2^{m-2} (6m - 5)$$

the arithmetic complexity per output is:

$m_r = 2m+4$   $a_r = 6m - 5$  $m_r + a_r = 8m - 1$

This scheme results in a slight increase in the arithmetic complexity. But such increase may be traded off by the reduction of the length of DFT's and of system delay.

# 3.4 Short length complex FIR filtering algorithms

Fast short length complex FIR filters find their applications both in the above schemes and in arbitrary length complex FIR filtering in the same manner as in real FIR filtering. This is our motivation to study these algorithms.

Eq.(3.18) is also applicable to complex filters. There are six simplest interpolation points in complex number domain  $\{0,1,-1,j,-j,\infty\}$ . Then we can construct 20 variants from these points for complex filtering. Further development of these variants is similar to (3.18) and will not be given here. We point out only that the F(2,2) algorithms with  $\{0,1,\infty\}$ ,  $\{0,-1,\infty\}$ ,  $\{0,-j,\infty\}$  and  $\{0,j,\infty\}$  as interpolation points require the least arithmetic complexity, i.e., 3 complex multiplications (cmults) and 4 complex additions (cadds) or (9 mults, 17 adds) in terms of real operations.

An optimal F(3,3) algorithm requires 5 interpolation points. Since there are six simplest interpolation points, we may choose 5 points out of them to construct an optimal algorithm. In [Bla84], we can find a radix-3 complex polynomial product algorithm. It uses  $\{0,1,-1,j,-j\}$  as interpolation points, leading to a (5 cmults, 15 cadds) algorithm. After overlap, it becomes an F(3,3) algorithm with (5 cmults, 17 cadds) or (15 mults, 51 adds).

However by using  $\{0,1,j,-j,\infty\}$  as interpolation points, we can obtain a better algorithm with less additions:

(a1) complex F(3,3) algorithm with (5 cmults, 15 cadds) or (15 mults, 45 adds)

a0=x0b0=h0a1=x2b1=h2a2=x0+x1+x2b2=h0+h1+h2a3=(x0-x2)+jx1b3=h0-h2+ih1a4 = (x0 - x2) - ix1b4=h0-h2-jh1 $mi=ai \cdot bi$ ; i=0,1,2,3,4u0=m0+m1u1=m3+m4u2=m3-m4u3 = -u0 + m2 $v0=m0+(u3+u1) z^{-3}$  $y1=u3-ju2+m1z^{-3}$ y2=u0+ju2-u1

For an optimal F(N,N) algorithm, we need (2N-1) interpolation points. As  $N\geq 4$  more than seven interpolation points are required. The six previous points are no longer sufficient. Which points should be chosen next? It seems  $\{ai\}=\{\pm 1\pm j\}$  are good candidates, since  $a_i^2=\pm 2j$  and  $a_i^4=-4$ . Only a few more additions are required with the increase of the exponent.

An F(5,5) algorithm using  $\{0,\pm 1,\pm j,\pm 1\pm j\}$  as interpolation points is given in the appendix. It requires (9 cmults, 77 cadds) or (27 mults, 181 adds). Although the F(5,5) is optimal in terms of multiplication count, it requires a great deal of additions. This increase in the number of additions may not justify the minimization of the number of multiplications in certain implementations where an addition and a multiplication require almost the same time.

Then it is desirable to construct some suboptimal algorithms which require more than 2N-1 multiplications but substantially less additions. An suboptimal F(4,4) algorithm can be derived by twice applying the eq.(3.18), leading to a (9 cmults, 20 cadds) or (27 mults, 67 adds) algorithm. Another way of obtaining suboptimal algorithm is proposed in [Bal86]. In their method, the derivation of the polynomial Q(z) at points  $\{0,\infty\}$  are used in order to use less interpolation points. For example, an F(4,4) algorithm can be constructed using the interpolation values at  $\{0,\pm1,\pm j,\infty\}$  and the derivation at  $\{0\}$ . The last

y3=p3

value (=x0h1+x1h0) requires two multiplications instead of one multiplication per interpolation points. But the number of additions can be reduced. We give this algorithm as follows:

(a2) complex F(4,4) algorithm with (8 cmults, 23 cadds) or (24 mults, 69 adds)

| a0=x0                  | b0=h0              |

|------------------------|--------------------|

| a1=x0                  | b1=h1              |

| a2=x1                  | b2=h0              |

| a3=x3                  | b3=h3              |

| a4=(x0+x2)+(x1+x3)     | b4=(h0+h2+h1+h3)/4 |

| a5=(x0+x2)-(x1+x3)     | b5=(h0+h2-h1-h3)/4 |

| a6=(x0-x2)+(x1-x3)     | b6=(h0-h2+h1-h3)/4 |

| a7=(x0-x2)-(x1-x3)     | b7=(h0-h2-h1+h3)/4 |

|                        |                    |

| mi=ai•bi; i=0,1,,8     |                    |

|                        |                    |

| u0=m4+m5               |                    |

| u1=m4-m5               |                    |

| u2=m6+m7               |                    |

| u3=m6-m7               |                    |

| p0=u0+u2               | •                  |

| p1=u1+u3               |                    |

| p2=u0-u2               |                    |

| p3=u1-u3               |                    |

| p4=m1+m2               |                    |

|                        |                    |

| $y0=m0+(p0-m0) z^{-4}$ |                    |

| $y1=p4+(p1-p4) z^{-4}$ |                    |

| $y2=(p2-m3)+m3 z^{-4}$ |                    |

In eq.(3.22) a length-L complex filter is transformed into 3 length-L real FIR filters instead of 4 by direct computation. Although fast real short length FIR filtering algorithms can be applied to compute the three length-L real FIR filters, we will show that deriving algorithms at first in complex domain results in more efficient ones.

Let us applying eq.(3.18) to complex filters. Then a length-L complex FIR filter can be computed by three length-L/2 complex FIR filters. Further applying eq.(3.22), we replace each of the three complex filters by three real ones of the same length. The resulting complexity is:

4 cadds + 3 (3 adds + 3 length-L/2 real filters) per two complex outputs = 17 adds+ 9 length-L/2 real filters per two complex outputs

If we first apply eq.(3.22) then eq.(3.18), the complexity will be:

3x2 adds + 3 (4 adds + 3 length-L/2 real filters) per two complex outputs = 18 adds + 9 length-L/2 real filters per two complex outputs

The first algorithm requires less additions.

The above discussion is in the case N=2. For higher N it is still more recommanded to apply short length complex FIR filtering algorithms first and eq.(3.22) then, since there are more simple interpolation points in the complex domain than in the real one.

We may apply the F(2,2) and F(4,4) algorithm to the scheme b) and c) of computing the length- $2^m$  FIR filter. The F(2,2) algorithm needs to consider two outputs together in the frequency domain so that  $2^m$  outputs of the filter should be computed together. By analogy, applying F(4,4) algorithm needs to compute  $2^m$  outputs of the filter together. The resulting arithmetic complexities are:

IIId) computing the length- $2^m$  real FIR filter using F(2,2) algorithm in frequency domain (per  $2^m$  outputs)

$Mr = 2^{m}(2m-1.5)+5$  $Ar = 2^{m}(6m-2.5)+3$

the arithmetic complexity per output

$mr=2m-1.5+5 \cdot 2^{-m}$   $ar =6m-2.5+3 \cdot 2^{-m}$  $mr+ar=8m-4+8 \cdot 2^{-m}$  To our surprise, this scheme results in reductions both in the number of multiplications and in the number of additions for m≥2, compared to the conventional scheme a).

IIIe) computing the length- $2^m$  real FIR filter using F(4,4) algorithm in frequency domain (per  $2^m$  outputs)

$Mr = 2^{m}(2m-2)+10$  $Ar = 2^{m}(6m+2.75)+1$

the arithmetic complexity per output

mr=  $2m-2+10 \cdot 2^{-m}$ ar =  $6m + 2.75 + 2^{-m}$ mr+ar= $8m+0.75+11 \cdot 2^{-m}$

Although this algorithm results in a reduction in the number of mltiplications, but it requires more additions and computes a block of 2<sup>m</sup> outputs together. Hence this scheme is less of interest than the others. It indicates also that the application of short length complex FIR filtering algorithms in such schemes should be limited. Direct computation of the filters in frequency domain may meet better trade-off between arithmetic complexity and structural regularity.

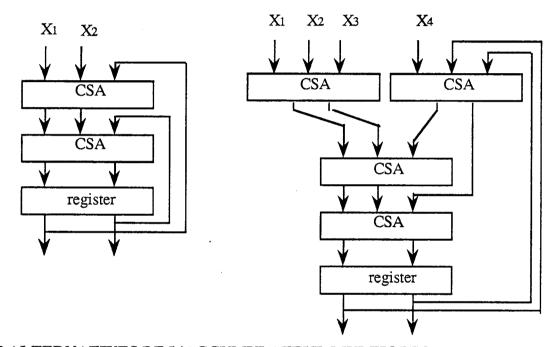

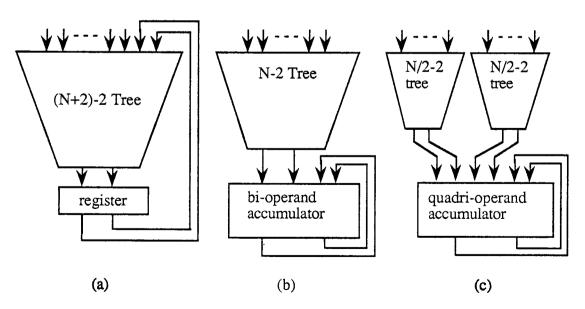

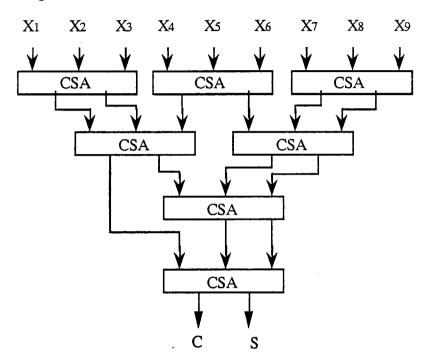

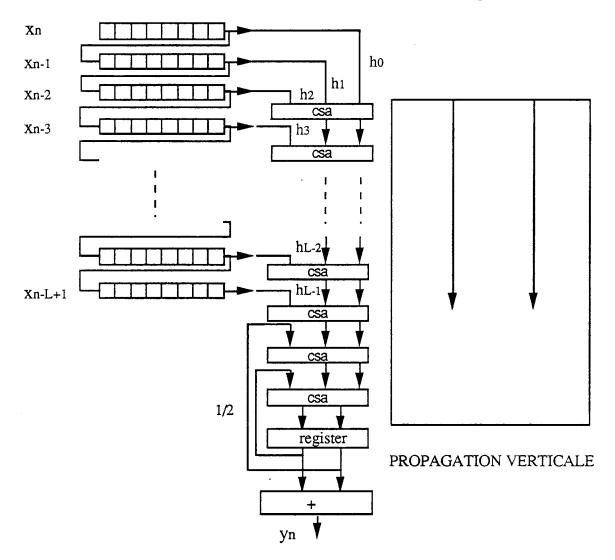

## 3.5 Remarks